Other Parts Discussed in Thread: OMAPL138

Hello TI team,

Let me explain the background before explaining the issue:

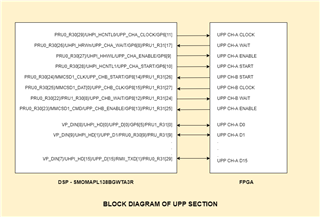

We have designed custom board with OMAPL138. We are trying to communicate with FPGA which is connected via UPP interface.

We are trying to receive data from FPGA via UPP interface. In DSP we are using the DDR2 memory for the receiving the data.

For receiving UPP data we have two global memory reserved in DDR2 as following,

volatile uint16_t u16_Rx_buffer[2][64]; // Address : 0xC3013B80 (which is DDR)

For copying and processing the received data we have temp buffer in DDR as following

volatile uint16_t temp_buffer;

Code snippet for configuring the DDR2 memory in UPP.

---------------------------------------------------------

unsigned char CycleIndex = 0;

#define UPP_TX_LINE_COUNT 1

#define UPP_RX_BYTE_PER_LINE_COUNT 128

---------------------------------------------------------

# following configuration is done while initialisation and every time in the UPP ISR when EOLI is received

uppRegs->UPID0 = (uint32_t)&u16_Rx_buffer[CycleIndex][0]; // DDR Address 0xC3013B80, Not fixed though

uppRegs->UPID1 = ((UPP_TX_LINE_COUNT << 16) | UPP_TX_BYTE_PER_LINE_COUNT);

uppRegs->UPID2 = 0;

if(CycleIndex == 0)

{

CycleIndex = 1;

}

else

{

CycleIndex = 0;

}

//Copying the UPP filled data for procesing (for testing we copied first byte only)

temp_buffer = u16_Rx_buffer[CycleIndex][0];

while(uppRegs->UPIS2 & 0x02){};

---------------------------------------------------------

ISSUE :

We are able to receive the data from FPGA and we could see in the memory browser window.

After receiving, we copied the u16_Rx_buffer to other temp buffer for processing.

After copying the received data, the first 64 Bytes memory is not getting filled from UPP in the succssive cycles. (Note : We configured DMA burst size as 64 Bytes).

Attaching the browser window for your reference (in snapshot we tried other memory for debugging but the issue remains same)