Hello Everyone,

I am trying to do a Peripheral Device Transfer (PDT) from an FPGA (FIFO on a Virtex-5) to a DSK6416. The data is 8-bit and fifo depth is 32.

The FULL flag of the FIFO will trigger a PDT (an EDMA event). The FULL flag of the FIFO is connected to EXT_INT7 which will trigger the EDMA event EDMA_EVT_EXTINT7 ( channel # 7 of C6416T ).

The FIFO worked perfectly in simulation as well as on the Virtex-5. It runs on ECLKOUT. ( I checked ECLKOUT by running a counter on the FPGA ).

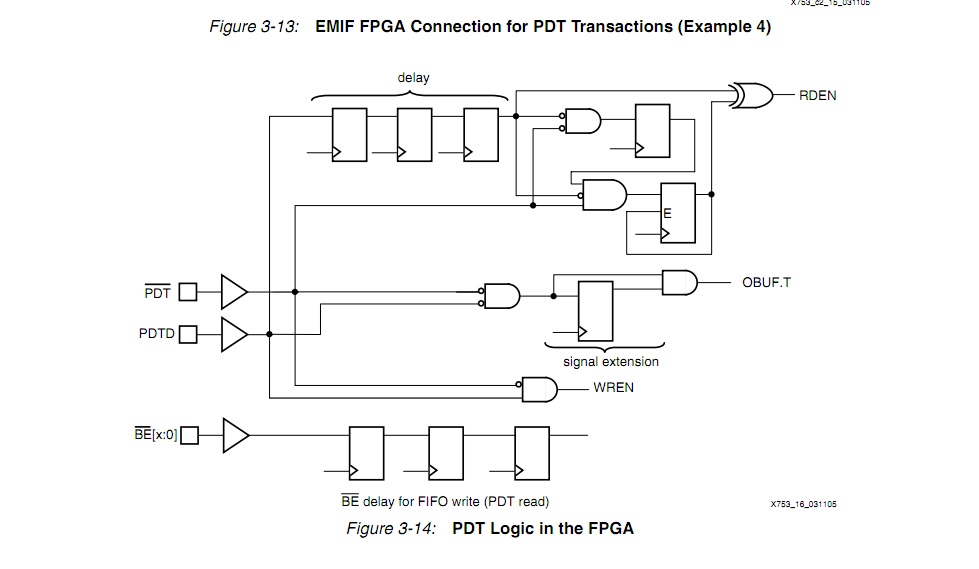

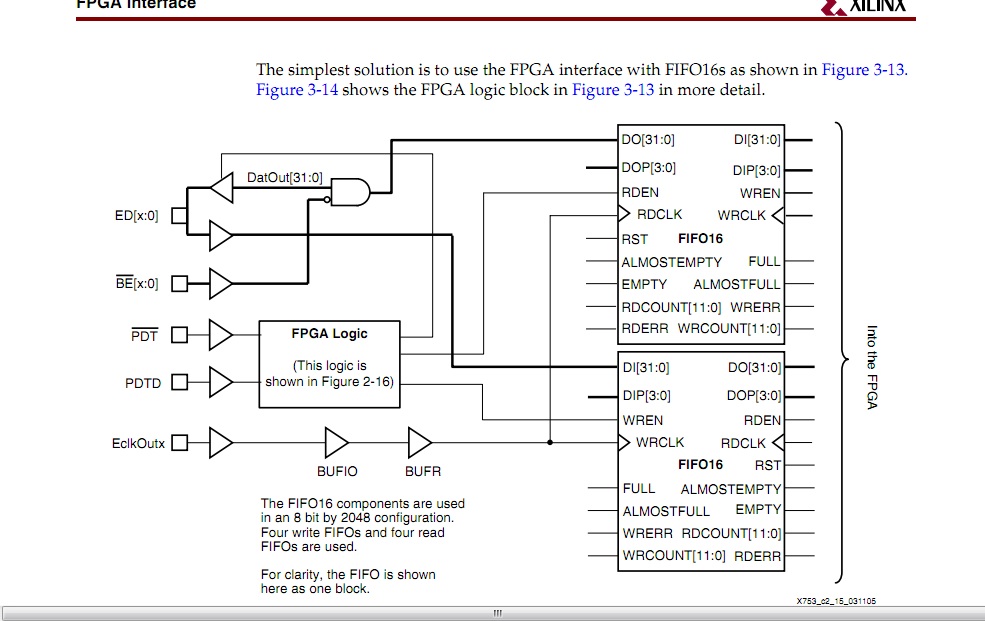

Connections between DSK and FPGA were setup according to XAPP753. (I've attached the screenshot of the setup.)

Initially I tested to see whether the FULL flag is interrupting the CPU or not and it did.

The problem is when I programmed the EDMA for channel 7, the FULL flag did not trigger the event. ( It did not set the EDMA EVENT SET register - ESR w.r.t channel 7 ).

So I tried to set the ESR (to trigger the event) by using EDMA_setChannel( handle) or EDMA_RSET(ESRL,value). This neither set the bit in the ESR nor did it change the corresponding bit in the Event Register (ERL). I tried another channel as well but that didn't work too. Does anyone have any idea what could be the reason ?

I have attached my code and a screenshot of the FPGA-DSP connection.

Even after setting up the CE space 0 as 8-bit wide SDRAM, BE signal wasn't driven LOW. Any help would be greatly appreciated. Thanks in advance.

Regards,

Varun Sridharan

/*

* Copyright 2003 by Texas Instruments Incorporated.

* All rights reserved. Property of Texas Instruments Incorporated.

* Restricted rights to use, duplicate or disclose this code are

* granted through contract. */

#include <stdio.h>

#include <csl.h>

#include <csl_cache.h>

#include <csl_edma.h>

#include <csl_timer.h>

#include <csl_irq.h>

#include <csl_edmahal.h>

#include <csl_emifa.h>

#include <csl_emifahal.h>

/*----------------------------------------------------------------------------*/

/* Pick which EDMA transfer completion interrupt we want to use */

#define TCCINTNUM 7

/* define the constants */

#define BUFF_SZ 32 /* data-pong buffer sizes in # of ints */

/* Create the buffers. We want to align the buffers to be cache friendly */

/* by aligning them on an L2 cache line boundary. */

#pragma DATA_SECTION (data, ".buffers");

#pragma DATA_ALIGN(data,8);

Uint8 data[BUFF_SZ];

Uint8 gTCC;

extern far void vectors();

void setupInterrupts(void);

void stopEdma(void); /* function used to stop EDMA */

/*-------------------------------------------------------------------------*/

/* declare the CSL objects */

EDMA_Handle hEdma; /* Handle for the EDMA channel */

EDMA_Config cfgpdt; /* EDMA configuration structure */

EMIFA_Config cfgemif;

/* Create the EDMA configuration structure for data transfers */

EDMA_Config cfgpdt = {

EDMA_OPT_RMK( /* Making Options parameter register - EDMA_OPT */

EDMA_OPT_PRI_LOW,

EDMA_OPT_ESIZE_8BIT,/* Element size :- */

EDMA_OPT_2DS_NO, /* Source dimension :-

EDMA_OPT_2DS_NO - 1-dimensional source

EDMA_OPT_2DS_YES - 2-dimensional source */

EDMA_OPT_SUM_INC, /* Source address update mode :-

EDMA_OPT_SUM_NONE - Fixed address mode

EDMA_OPT_SUM_INC - Increment address mode

EDMA_OPT_SUM_DEC - Decrement address mode

EDMA_OPT_SUM_IDX - Address modified by element

index or frame Index */

EDMA_OPT_2DD_NO, /* Destination dimension :-

EDMA_OPT_2DD_NO - 1-dimensional source

EDMA_OPT_2DD_YES - 2-dimensional source */

EDMA_OPT_DUM_INC, /* Destination address update mode :-

EDMA_OPT_DUM_NONE - Fixed address mode

EDMA_OPT_DUM_INC - Increment address mode */

EDMA_OPT_TCINT_YES, /* Transfer complete interrupt :-

EDMA_OPT_TCINT_NO - Indication disabled

EDMA_OPT_TCINT_YES - Indication enabled */

EDMA_OPT_TCC_OF(0),/* Transfer complete code */

EDMA_OPT_TCCM_OF(0),

EDMA_OPT_ATCINT_NO,

EDMA_OPT_ATCC_OF(0),

EDMA_OPT_PDTS_DISABLE,

EDMA_OPT_PDTD_ENABLE, /*PDT Write Enabled */

EDMA_OPT_LINK_NO, /* Linking of event parameters */

EDMA_OPT_FS_YES /* Frame synchronization

EDMA_OPT_FS_NO - Channel is element/array

synchronized

EDMA_OPT_FS_YES - Channel is frame synchronized*/

),

EDMA_SRC_OF(data),/* Source address register

- source address */

EDMA_CNT_RMK(

EDMA_CNT_ELECNT_OF(32), /* Transfer count parameter

BUFF_SZ - buffer sizes in # of ints */

EDMA_CNT_FRMCNT_OF(0)),

EDMA_DST_OF(data), /* Destination address parameter

data - destination address */

EDMA_IDX_OF(0x00000000),/* Index parameter */

EDMA_RLD_OF(0x00000000) /* Count reload/link parameter */

};

/* EMIFA Setup */

EMIFA_Config cfgemif = {

0x00012774,

0xFFFFFF83, /* MTYPE is set to 8-bit SDRAM */

0xFFFFFF03,

0x23228C22,

0x23228C22,

0x46115000,

0x0026A750,

0x001FAF4D,

0x00000002,

0x00000002,

0x00000002,

0x00000002

};

Uint32 fieldval, MTYPEval, val;

/*----------------------------------------------------------------------------*/

void main(){

/* initialize the CSL library */

CSL_init();

MTYPEval = EMIFA_FGET(CECTL0,MTYPE);

printf("\nMTYPE in CECTL0 field value is %d\n",MTYPEval);

EMIFA_FSET(CECTL0,MTYPE,8); // sets CE0 space to 8bit SDRAM

EMIFA_FSET(PDTCTL,PDTWL,1); /* PDT signal Latency */

printf("\nMTYPE in CECTL0 field value is %d\n",EMIFA_FGET(CECTL0,MTYPE));

gTCC = EDMA_intAlloc(7); /* allocate for CIPR[7] */

printf("\n%d\n", gTCC);

cfgpdt.opt = EDMA_FMK(OPT,TCC,gTCC);

/* from a previous run of the program. */

setupInterrupts(); /* defined below */

EDMA_clearPram(0x00000000);

/* Open EDMA channel associated with . */

hEdma = EDMA_open(EDMA_CHA_EXTINT7, EDMA_OPEN_RESET);

/* Program the EDMA channel with the configuration structure */

EDMA_config(hEdma, &cfgpdt);

/* EMIF config */

EMIFA_config(&cfgemif);

/* Enable the related interrupts */

IRQ_enable(IRQ_EVT_EXTINT7);

//IRQ_enable(IRQ_EVT_EDMAINT);

EDMA_intEnable(gTCC);

/* Enable the EDMA channel */

EDMA_enableChannel(hEdma);

while(1);

}

void setupInterrupts(void)

{

IRQ_setVecs(vectors); /* point to the IRQ vector table */

IRQ_nmiEnable();

IRQ_globalEnable();

IRQ_map(IRQ_EVT_EXTINT7, 7);

//IRQ_map(IRQ_EVT_EDMAINT, 8);

IRQ_reset(IRQ_EVT_EDMAINT);

}

/* ISR */

interrupt void

c_int08(void)

{

printf("\nEntered ISR .. CHECK\n");

EDMA_setChannel(hEdma);

while(1); /* At this point when I check, ESRL and ERL are not SET */

printf ("\nProcessed Interrupts.....");

stopEdma();

exit(0);

return;

} /* end c_int08 */

void stopEdma(void) {

/*Disable interrupts and close EDMA channel*/

IRQ_disable(IRQ_EVT_EXTINT7);

EDMA_RSET(CCER,0x00000000);

EDMA_intDisable(gTCC);

EDMA_close(hEdma);

EDMA_resetAll();

}