Other Parts Discussed in Thread: SYSCONFIG

TDA4VM

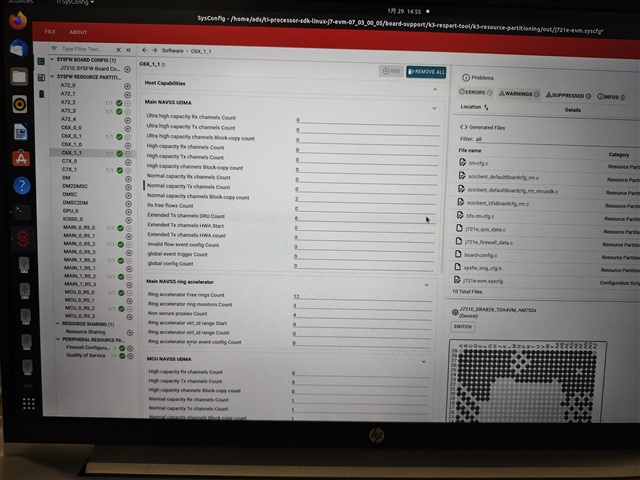

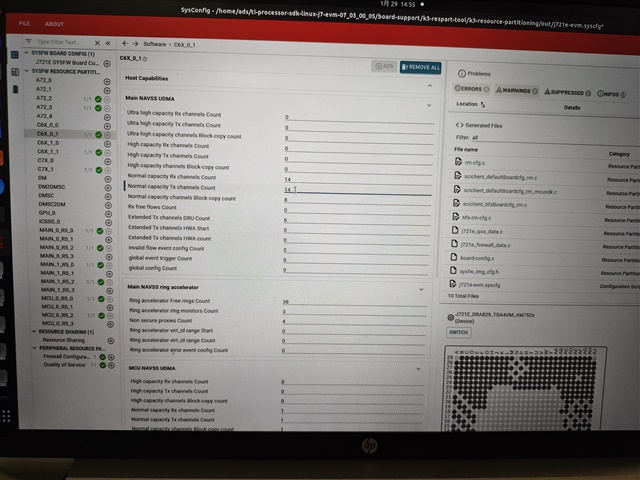

SDK 07_03_00_07

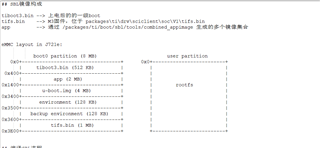

DSP C6x_1

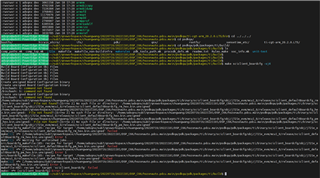

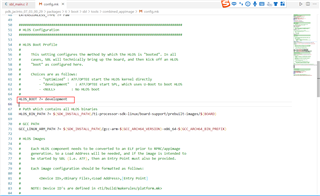

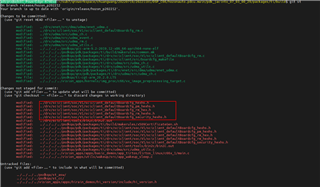

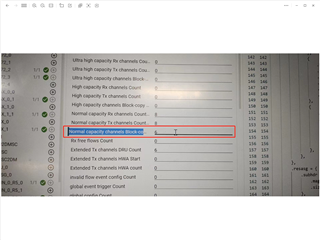

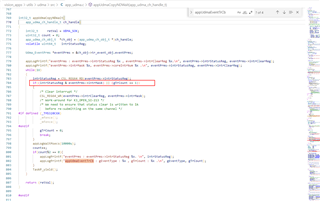

1. i use appUdmaCopyNDGetHandle() function to get dma channel , but I find that when i call more than 8 times, an error (VINTR alloc failed )has occurred. as the image show.

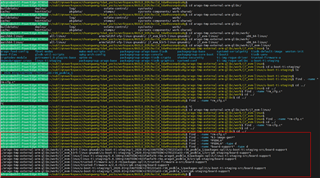

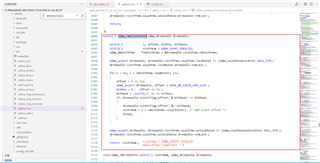

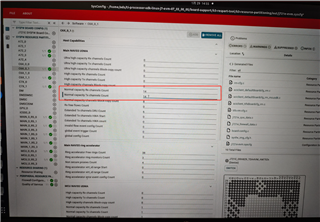

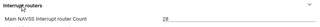

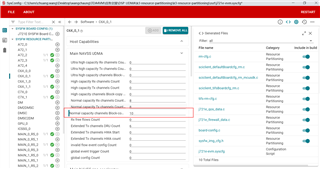

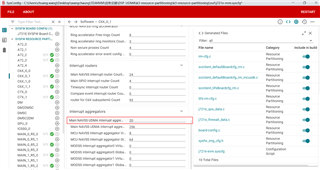

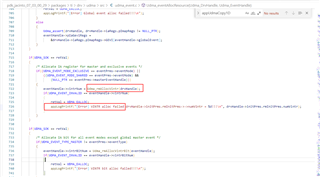

and i find it because rmInitPrms->numVintr is 8, so I can't call it more than 8 times. as image show .

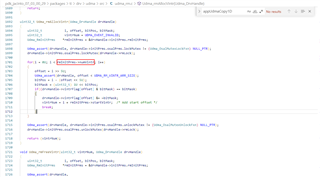

2. I would like to know if I can configure this (rmInitPrms->numVintr) and how