Other Parts Discussed in Thread: TIDEP-01012

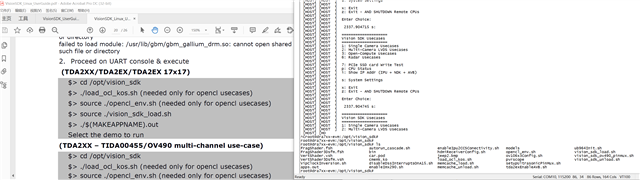

With TIDEP-01012 and TIDEP-01017 EVM board, I run ./disableDssInterruptsOnA15.sh

(1) In ./disableDssInterruptsOnA15.sh, is it right to write `omapconf clear bit $crossbar 0`?

do you think `` should be deleted? only omapconf clear bit $crossbar 0 is ok?

(2) what is DISPC? omapconf dump crossbar irq mpu | grep DISPC | awk -F" " '{ print $4}'

There is no DISPC at all when omapconf dump crossbar irq mpu runs.

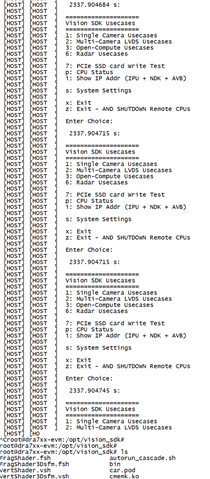

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk# ./disableDssInterruptsOnA15.sh

./disableDssInterruptsOnA15.sh: line 11: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 12: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 13: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 14: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 15: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 16: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 17: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 18: COMMANDS: command not found

./disableDssInterruptsOnA15.sh: line 19: COMMANDS: command not found

updated value is

COMMANDS

### WARNING ###: use the following [read | write | set bit | clear bit | dump] commands at your own risk!

No address check done, may generate:

- bus error (invalid or not accessible <physical address>,

- platform crash/hang (bad <value>).

Read any OMAP memory address (register), given its <physical address> or <name> as listed in TRM.

Write <value> at any OMAP memory address (register), given its <physical address> or <name> as listed in TRM.

Set bit at <position> into any OMAP memory address (register), given its <physical address> or <name> as listed in TRM.

Clear bit at <position> into any OMAP memory address (register), given its <physical address> or <name> as listed in TRM.

Dump a range of OMAP memory addresses, from <start address> to <end address>.

Note all addresses within given range must be valid and accessible.

### WARNING ###: use the following I2C [read | write] commands at your own risk!

No address check done, may generate:

- I2C bus error (invalid or not accessible <physical address>,

- platform crash/hang (bad <value>).

Read I2C register at address <addr> from I2C chip at <chip-addr> on I2C <bus>.

Write <value> in I2C register at address <addr> from I2C chip at <chip-addr> on I2C <bus>.

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk# cat ./disableDssInterruptsOnA15.sh

#!/bin/sh

#disable display interruts from a15

# this is a temporary patch

# Identified that 20 is irq number for DISPC_IRQ on A15.

# grep for crossbar req and disable it

# update ipks in case of j6-eco

crossbar=`omapconf dump crossbar irq mpu | grep DISPC | awk -F" " '{ print $4}'`

# modify the last 4 bits

`omapconf clear bit $crossbar 0`

`omapconf clear bit $crossbar 1`

`omapconf clear bit $crossbar 2`

`omapconf clear bit $crossbar 3`

`omapconf clear bit $crossbar 4`

`omapconf clear bit $crossbar 5`

`omapconf clear bit $crossbar 6`

`omapconf clear bit $crossbar 7`

`omapconf clear bit $crossbar 8`

val=`omapconf read $crossbar 2>&1 | grep -v omapconf`

echo "updated $crossbar value is $val"

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk#

root@dra7xx-evm:/opt/vision_sdk# omapconf dump crossbar irq mpu

OMAPCONF (rev v1.73-17-g578778b built Tue May 14 01:27:24 IST 2019)

HW Platform:

Generic DRA74X (Flattened Device Tree)

DRA75X ES2.0 GP Device (STANDARD performance (1.0GHz))

TPS659038 ES UNKNOWN

SW Build Details:

Build:

Version: _____ _____ _ _

Kernel:

Version: 4.4.84-00041-g84382ab

Author: x0284921@bangvideoapps02

Toolchain: gcc version 5.3.1 20160113 (Linaro GCC 5.3-2016.02)

Type: #1 SMP PREEMPT

Date: Mon Aug 5 14:52:40 IST 2019

|----------------------------------------------------------------------------------------------------------------------------------------------|

| mpu IRQ Crossbar Dump |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Index | Addr | Val | Name | Source | Description |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | N/A | N/A | MPU_CLUSTER_IRQ_INTERR | MPU_CLUSTER | Illegal writes to interrupt controller memory map region |

| 1 | N/A | N/A | CS_CTI_MPU_C0_IRQ | MPU_C0_CS_CTI | TRIGOUT[6] of Cross Trigger Interface 0 (CTI0) |

| 2 | N/A | N/A | CS_CTI_MPU_C1_IRQ | MPU_C1_CS_CTI | TRIGOUT[6] of Cross Trigger Interface 1 (CTI1) |

| 3 | N/A | N/A | MPU_CLUSTER_IRQ_AXIERR | MPU_CLUSTER | Error indication for AXI write transactions with a BRESP err |

| 4 | 0x4A002A48 | 0 | reserved | reserved | N/A |

| 5 | N/A | N/A | WD_TIMER_MPU_C0_IRQ_WARN | MPU_WD_TIMER | MPU_WD_TIMER channel 0 warning interrupt |

| 6 | N/A | N/A | WD_TIMER_MPU_C1_IRQ_WARN | MPU_WD_TIMER | MPU_WD_TIMER channel 1 warning interrupt |

| 7 | 0x4A002A4A | 0 | reserved | reserved | N/A |

| 8 | 0x4A002A4C | 0 | reserved | reserved | N/A |

| 9 | 0x4A002A4E | 0 | reserved | reserved | N/A |

| 10 | 0x4A002A50 | 5 | L3_MAIN_IRQ_APP_ERR | L3_MAIN | L3_MAIN application or non-attributable error |

| 11 | 0x4A002A52 | 0 | reserved | reserved | N/A |

| 12 | 0x4A002A54 | 0 | reserved | reserved | N/A |

| 13 | 0x4A002A56 | 0 | reserved | reserved | N/A |

| 14 | 0x4A002A58 | 0 | reserved | reserved | N/A |

| 15 | 0x4A002A5A | 0 | reserved | reserved | N/A |

| 16 | 0x4A002A5C | 0 | reserved | reserved | N/A |

| 17 | 0x4A002A5E | 0 | reserved | reserved | N/A |

| 18 | 0x4A002A60 | 0 | reserved | reserved | N/A |

| 19 | 0x4A002A62 | 0 | reserved | reserved | N/A |

| 20 | 0x4A002A64 | 0 | reserved | reserved | N/A |

| 21 | 0x4A002A66 | 0 | reserved | reserved | N/A |

| 22 | 0x4A002A68 | 0 | reserved | reserved | N/A |

| 23 | 0x4A002A6A | 0 | reserved | reserved | N/A |

| 24 | 0x4A002A6C | 0 | reserved | reserved | N/A |

| 25 | 0x4A002A6E | 0 | reserved | reserved | N/A |

| 26 | 0x4A002A70 | 0 | reserved | reserved | N/A |

| 27 | 0x4A002A72 | 0 | reserved | reserved | N/A |

| 28 | 0x4A002A74 | 0 | reserved | reserved | N/A |

| 29 | 0x4A002A76 | 0 | reserved | reserved | N/A |

| 30 | 0x4A002A78 | 0 | reserved | reserved | N/A |

| 31 | 0x4A002A7A | 0 | reserved | reserved | N/A |

| 32 | 0x4A002A7C | 0 | reserved | reserved | N/A |

| 33 | 0x4A002A7E | 0 | reserved | reserved | N/A |

| 34 | 0x4A002A80 | 0 | reserved | reserved | N/A |

| 35 | 0x4A002A82 | 0 | reserved | reserved | N/A |

| 36 | 0x4A002A84 | 0 | reserved | reserved | N/A |

| 37 | 0x4A002A86 | 0 | reserved | reserved | N/A |

| 38 | 0x4A002A88 | 0 | reserved | reserved | N/A |

| 39 | 0x4A002A8A | 0 | reserved | reserved | N/A |

| 40 | 0x4A002A8C | 0 | reserved | reserved | N/A |

| 41 | 0x4A002A8E | 0 | reserved | reserved | N/A |

| 42 | 0x4A002A90 | 0 | reserved | reserved | N/A |

| 43 | 0x4A002A92 | 0 | reserved | reserved | N/A |

| 44 | 0x4A002A94 | 0 | reserved | reserved | N/A |

| 45 | 0x4A002A96 | 0 | reserved | reserved | N/A |

| 46 | 0x4A002A98 | 0 | reserved | reserved | N/A |

| 47 | 0x4A002A9A | 0 | reserved | reserved | N/A |

| 48 | 0x4A002A9C | 0 | reserved | reserved | N/A |

| 49 | 0x4A002A9E | 0 | reserved | reserved | N/A |

| 50 | 0x4A002AA0 | 0 | reserved | reserved | N/A |

| 51 | 0x4A002AA2 | 0 | reserved | reserved | N/A |

| 52 | 0x4A002AA4 | 0 | reserved | reserved | N/A |

| 53 | 0x4A002AA6 | 0 | reserved | reserved | N/A |

| 54 | 0x4A002AA8 | 0 | reserved | reserved | N/A |

| 55 | 0x4A002AAA | 0 | reserved | reserved | N/A |

| 56 | 0x4A002AAC | 0 | reserved | reserved | N/A |

| 57 | 0x4A002AAE | 0 | reserved | reserved | N/A |

| 58 | 0x4A002AB0 | 0 | reserved | reserved | N/A |

| 59 | 0x4A002AB2 | 0 | reserved | reserved | N/A |

| 60 | 0x4A002AB4 | 0 | reserved | reserved | N/A |

| 61 | 0x4A002AB6 | 0 | reserved | reserved | N/A |

| 62 | 0x4A002AB8 | 0 | reserved | reserved | N/A |

| 63 | 0x4A002ABA | 0 | reserved | reserved | N/A |

| 64 | 0x4A002ABC | 0 | reserved | reserved | N/A |

| 65 | 0x4A002ABE | 0 | reserved | reserved | N/A |

| 66 | 0x4A002AC0 | 0 | reserved | reserved | N/A |

| 67 | 0x4A002AC2 | 0 | reserved | reserved | N/A |

| 68 | 0x4A002AC4 | 0 | reserved | reserved | N/A |

| 69 | 0x4A002AC6 | 0 | reserved | reserved | N/A |

| 70 | 0x4A002AC8 | 0 | reserved | reserved | N/A |

| 71 | 0x4A002ACA | 0 | reserved | reserved | N/A |

| 72 | 0x4A002ACC | 0 | reserved | reserved | N/A |

| 73 | 0x4A002ACE | 0 | reserved | reserved | N/A |

| 74 | 0x4A002AD0 | 0 | reserved | reserved | N/A |

| 75 | 0x4A002AD2 | 0 | reserved | reserved | N/A |

| 76 | 0x4A002AD4 | 0 | reserved | reserved | N/A |

| 77 | 0x4A002AD6 | 147 | DSP2_IRQ_MMU1 | DSP2 | DSP2 MMU1 interrupt |

| 78 | 0x4A002AD8 | 146 | DSP2_IRQ_MMU0 | DSP2 | DSP2 MMU0 interrupt |

| 79 | 0x4A002ADA | 47 | RNG_IRQ | RNG | RNG interrupt |

| 80 | 0x4A002ADC | 46 | SHA2MD5_1_IRQ_P | SHA2MD5_1 | SHA2MD5_1 interrupt on HIB2 |

| 81 | 0x4A002ADE | 77 | DES3DES_IRQ_P | DES3DES | DES3DES public interrupt |

| 82 | 0x4A002AE0 | 59 | reserved | reserved | N/A |

| 83 | 0x4A002AE2 | 80 | AES1_IRQ_P | AES1 | AES1 public interrupt |

| 84 | 0x4A002AE4 | 222 | DCAN1_IRQ_INT0 | DCAN1 | DCAN1 interrupt 0 |

| 85 | 0x4A002AE6 | 337 | GMAC_SW_IRQ_MISC_PULSE | GMAC_SW | GMAC_SW miscellaneous interrupt |

| 86 | 0x4A002AE8 | 336 | GMAC_SW_IRQ_TX_PULSE | GMAC_SW | GMAC_SW transmit interrupt |

| 87 | 0x4A002AEA | 335 | GMAC_SW_IRQ_RX_PULSE | GMAC_SW | GMAC_SW receive interrupt |

| 88 | 0x4A002AEC | 334 | GMAC_SW_IRQ_RX_THRESH_PULSE | GMAC_SW | GMAC_SW receive threshold interrupt |

| 89 | 0x4A002AEE | 160 | McASP8_IRQ_AREVT | McASP8 | McASP8 receive interrupt |

| 90 | 0x4A002AF0 | 161 | McASP8_IRQ_AXEVT | McASP8 | McASP8 transmit interrupt |

| 91 | 0x4A002AF2 | 15 | GPMC_IRQ | GPMC | GPMC interrupt |

| 92 | 0x4A002AF4 | 1 | ELM_IRQ | ELM | Error location process completion interrupt |

| 93 | 0x4A002AF6 | 87 | USB2_IRQ_INTR1 | USB2 | USB2 interrupt 1 |

| 94 | 0x4A002AF8 | 72 | USB1_IRQ_INTR1 | USB1 | USB1 interrupt 1 |

| 95 | 0x4A002AFA | 217 | RTC_SS_IRQ_ALARM | RTC_SS | RTC_SS alarm interrupt |

| 96 | 0x4A002AFC | 49 | SATA_IRQ | SATA | SATA interrupt |

| 97 | 0x4A002AFE | 343 | QSPI_IRQ | QSPI | QSPI interrupt |

| 98 | 0x4A002B00 | 396 | IPU2_IRQ_MMU | IPU2 | IPU2 MMU interrupt |

| 99 | 0x4A002B02 | 395 | IPU1_IRQ_MMU | IPU1 | IPU1 MMU interrupt |

| 100 | 0x4A002B04 | 145 | DSP1_IRQ_MMU1 | DSP1 | DSP1 MMU1 interrupt |

| 101 | 0x4A002B06 | 23 | DSP1_IRQ_MMU0 | DSP1 | DSP1 MMU0 interrupt |

| 102 | 0x4A002B08 | 81 | MMC2_IRQ | MMC2 | MMC2 interrupt |

| 103 | 0x4A002B0A | 78 | MMC1_IRQ | MMC1 | MMC1 interrupt |

| 104 | 0x4A002B0C | 56 | I2C3_IRQ | I2C3 | I2C3 interrupt |

| 105 | 0x4A002B0E | 51 | I2C1_IRQ | I2C1 | I2C1 interrupt |

| 106 | 0x4A002B10 | 120 | BB2D_IRQ | BB2D | BB2D interrupt |

| 107 | 0x4A002B12 | 16 | GPU_IRQ | GPU | GPU interrupt |

| 108 | 0x4A002B14 | 108 | DMM_IRQ | DMM | DMM interrupt |

| 109 | 0x4A002B16 | 342 | TIMER16_IRQ | TIMER16 | TIMER16 interrupt |

| 110 | 0x4A002B18 | 341 | TIMER15_IRQ | TIMER15 | TIMER15 interrupt |

| 111 | 0x4A002B1A | 340 | TIMER14_IRQ | TIMER14 | TIMER14 interrupt |

| 112 | 0x4A002B1C | 339 | TIMER13_IRQ | TIMER13 | TIMER13 interrupt |

| 113 | 0x4A002B1E | 90 | TIMER12_IRQ | TIMER12 | TIMER12 interrupt |

| 114 | 0x4A002B20 | 42 | TIMER11_IRQ | TIMER11 | TIMER11 interrupt |

| 115 | 0x4A002B22 | 41 | TIMER10_IRQ | TIMER10 | TIMER10 interrupt |

| 116 | 0x4A002B24 | 40 | TIMER9_IRQ | TIMER9 | TIMER9 interrupt |

| 117 | 0x4A002B26 | 39 | TIMER8_IRQ | TIMER8 | TIMER8 interrupt |

| 118 | 0x4A002B28 | 38 | TIMER7_IRQ | TIMER7 | TIMER7 interrupt |

| 119 | 0x4A002B2A | 37 | TIMER6_IRQ | TIMER6 | TIMER6 interrupt |

| 120 | 0x4A002B2C | 36 | TIMER5_IRQ | TIMER5 | TIMER5 interrupt |

| 121 | 0x4A002B2E | 35 | TIMER4_IRQ | TIMER4 | TIMER4 interrupt |

| 122 | 0x4A002B30 | 34 | TIMER3_IRQ | TIMER3 | TIMER3 interrupt |

| 123 | 0x4A002B32 | 33 | TIMER2_IRQ | TIMER2 | TIMER2 interrupt |

| 124 | 0x4A002B34 | 256 | MAILBOX6_IRQ_USER3 | MAILBOX6 | Mailbox 6 user 3 interrupt |

| 125 | 0x4A002B36 | 255 | MAILBOX6_IRQ_USER2 | MAILBOX6 | Mailbox 6 user 2 interrupt |

| 126 | 0x4A002B38 | 254 | MAILBOX6_IRQ_USER1 | MAILBOX6 | Mailbox 6 user 1 interrupt |

| 127 | 0x4A002B3A | 253 | MAILBOX6_IRQ_USER0 | MAILBOX6 | Mailbox 6 user 0 interrupt |

| 128 | 0x4A002B3C | 252 | MAILBOX5_IRQ_USER3 | MAILBOX5 | Mailbox 5 user 3 interrupt |

| 129 | 0x4A002B3E | 251 | MAILBOX5_IRQ_USER2 | MAILBOX5 | Mailbox 5 user 2 interrupt |

| 130 | 0x4A002B40 | 250 | MAILBOX5_IRQ_USER1 | MAILBOX5 | Mailbox 5 user 1 interrupt |

| 131 | N/A | N/A | MPU_CLUSTER_IRQ_PMU_C0 | MPU_CLUSTER | MPU core 0 PMU interrupt |

| 132 | N/A | N/A | MPU_CLUSTER_IRQ_PMU_C1 | MPU_CLUSTER | MPU core 1 PMU interrupt |

| 133 | 0x4A002B42 | 0 | reserved | reserved | N/A |

| 134 | 0x4A002B44 | 249 | MAILBOX5_IRQ_USER0 | MAILBOX5 | Mailbox 5 user 0 interrupt |

| 135 | 0x4A002B46 | 69 | UART3_IRQ | UART3 | UART3 interrupt |

| 136 | 0x4A002B48 | 68 | UART2_IRQ | UART2 | UART2 interrupt |

| 137 | 0x4A002B4A | 67 | UART1_IRQ | UART1 | UART1 interrupt |

| 138 | 0x4A002B4C | 116 | GPIO8_IRQ_1 | GPIO8 | GPIO8 interrupt 1 |

| 139 | 0x4A002B4E | 0 | reserved | reserved | N/A |

| 140 | 0x4A002B50 | 0 | reserved | reserved | N/A |

| 141 | 0x4A002B52 | 29 | GPIO6_IRQ_1 | GPIO6 | GPIO6 interrupt 1 |

| 142 | 0x4A002B54 | 27 | GPIO4_IRQ_1 | GPIO4 | GPIO4 interrupt 1 |

| 143 | 0x4A002B56 | 26 | GPIO3_IRQ_1 | GPIO3 | GPIO3 interrupt 1 |

| 144 | 0x4A002B58 | 24 | GPIO1_IRQ_1 | GPIO1 | GPIO1 interrupt 1 |

| 145 | 0x4A002B5A | 371 | EDMA_TC1_IRQ_ERR | EDMA | TC1 EDMA TPTC1 error interrupt |

| 146 | 0x4A002B5C | 370 | EDMA_TC0_IRQ_ERR | EDMA | TC0 EDMA TPTC0 error interrupt |

| 147 | 0x4A002B5E | 359 | EDMA_TPCC_IRQ_ERR | EDMA | TPCC EDMA TPCC error interrupt |

| 148 | 0x4A002B60 | 360 | EDMA_TPCC_IRQ_MP | EDMA | TPCC EDMA TPCC memory protection interrupt |

| 149 | 0x4A002B62 | 361 | EDMA_TPCC_IRQ_REGION0 | EDMA | TPCC EDMA TPCC region 0 interrupt |

| 150 | 0x4A002B64 | 10 | DMA_SYSTEM_IRQ_3 | DMA_SYSTEM | System DMA interrupt 3 |

| 151 | 0x4A002B66 | 9 | DMA_SYSTEM_IRQ_2 | DMA_SYSTEM | System DMA interrupt 2 |

| 152 | 0x4A002B68 | 8 | DMA_SYSTEM_IRQ_1 | DMA_SYSTEM | System DMA interrupt 1 |

| 153 | 0x4A002B6A | 7 | DMA_SYSTEM_IRQ_0 | DMA_SYSTEM | System DMA interrupt 0 |

| 154 | 0x4A002B6C | 121 | CTRL_MODULE_CORE_IRQ_THERMAL_ALERT | CTRL_MODULE | CTRL_MODULE thermal alert interrupt |

| 155 | 0x4A002B6E | 233 | PCIe_SS1_IRQ_INT1 | PCIe_SS1 | PCIe_SS1 interrupt 1 |

| 156 | 0x4A002B70 | 232 | PCIe_SS1_IRQ_INT0 | PCIe_SS1 | PCIe_SS1 interrupt 0 |

| 157 | 0x4A002B72 | 6 | PRM_IRQ_MPU | PRM | PRCM interrupt to MPU |

| 158 | 0x4A002B74 | 4 | L3_MAIN_IRQ_DBG_ERR | L3_MAIN | L3_MAIN debug error |

| 159 | 0x4A002B76 | 32 | TIMER1_IRQ | TIMER1 | TIMER1 interrupt |

|----------------------------------------------------------------------------------------------------------------------------------------------|

root@dra7xx-evm:/opt/vision_sdk#