Other Parts Discussed in Thread: SYSCONFIG

Hi ,

We want to attain the communication between the GPMC and NoR flash kind of slave and we're dooing 16 bit access non multipluxed asynchrounous read write under following config

| GPMC | Ball Pin | Address | Value |

| gpmc_a17 | D8 | 0x4A00 3554 | 0x5000E |

| gpmc_a16 | C5 | 0x4A00 3498 | 0x50002 |

| gpmc_a15 | D6 | 0x4A00 3494 | 0x50002 |

| gpmc_a14 | E7 | 0x4A00 3490 | 0x50002 |

| gpmc_a13 | A4 | 0x4A00 348C | 0x50002 |

| gpmc_a12 | G1 | 0x4A00 3460 | 0x50000 |

| gpmc_a11 | L3 | 0x4A00 346C | 0x50000 |

| gpmc_a10 | J2 | 0x4A00 3468 | 0x50000 |

| gpmc_a9 | H1 | 0x4A00 3464 | 0x50000 |

| gpmc_a8 | K4 | 0x4A00 3460 | 0x50000 |

| gpmc_a7 | K1 | 0x4A00 345C | 0x50000 |

| gpmc_a6 | J1 | 0x4A00 3458 | 0x50000 |

| gpmc_a5 | K2 | 0x4A00 3454 | 0x50000 |

| gpmc_a4 | K3 | 0x4A00 3450 | 0x50000 |

| gpmc_a3 | H6 | 0x4A00 34D4 | 0x70005 |

| gpmc_a2 | L2 | 0x4A00 3448 | 0x50000 |

| gpmc_a1 | M2 | 0x4A00 3444 | 0x50000 |

| gpmc_a0 | M1 | 0x4A00 3440 | 0x50000 |

| gpmc_ad15 | B4 | 0x4A00 343C | 0x50000 |

| gpmc_ad14 | A3 | 0x4A00 3438 | 0x50000 |

| gpmc_ad13 | C4 | 0x4A00 3434 | 0x50000 |

| gpmc_ad12 | C3 | 0x4A00 3430 | 0x50000 |

| gpmc_ad11 | B3 | 0x4A00 342C | 0x50000 |

| gpmc_ad10 | A2 | 0x4A00 3428 | 0x50000 |

| gpmc_ad9 | D3 | 0x4A00 3424 | 0x50000 |

| gpmc_ad8 | C2 | 0x4A00 3420 | 0x50000 |

| gpmc_ad7 | B2 | 0x4A00 341C | 0x50000 |

| gpmc_ad6 | B1 | 0x4A00 3418 | 0x50000 |

| gpmc_ad5 | D2 | 0x4A00 3414 | 0x50000 |

| gpmc_ad4 | D1 | 0x4A00 3410 | 0x50000 |

| gpmc_ad3 | C1 | 0x4A00 340C | 0x50000 |

| gpmc_ad2 | E1 | 0x4A00 3408 | 0x50000 |

| gpmc_ad1 | E2 | 0x4A00 3404 | 0x50000 |

| gpmc_ad0 | F1 | 0x4A00 3400 | 0x50000 |

| gpmc_wait0 | F6 | 0x4A00 34D8 | 0x70000 |

| gpmc_cs0 | F3 | 0x4A00 34B4 | 0x70000 |

| gpmc_cs1 | A6 | 0x4A00 34B0 | 0x70000 |

| gpmc_cs3 | G3 | 0x4A00 34BC | 0x70000 |

| gpmc_cs7 | L4 | 0x4A00 34C0 | 0x70001 |

| gpmc_oen_ren | G5 | 0x4A00 34C8 | 0x70000 |

| gpmc_wen | G6 | 0x4A00 34CC | 0x70000 |

| Configuration of GPMC | |||

| gpmc_sysconfig | 0x50000010 | 0x00000008 | |

| gpmc_irqstatus | 0x5000001C | 0x00000100 | |

| gpmc_timeout_ctrl | 0x50000040 | 0x00001FF0 | |

| gpmc_config | 0x50000050 | 0x00000100 | |

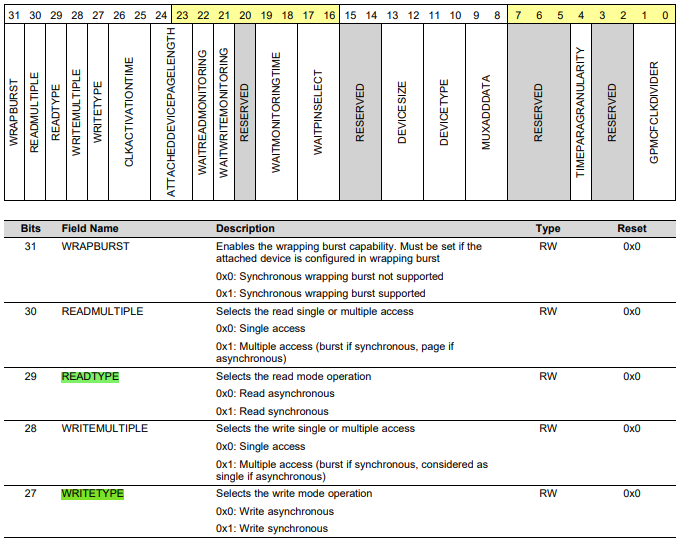

| gpmc_config_1 | 0x50000060 | 0x7A641000 | |

| gpmc_config_2 | 0x50000064 | 0x00081D00 | |

| gpmc_config_3 | 0x50000068 | 0x00010100 | |

| gpmc_config_4 | 0x5000006C | 0x08021D03 | |

| gpmc_config_5 | 0x50000070 | 0x01081F1F | |

| gpmc_config_6 | 0x50000074 | 0x820302C0 | |

| gpmc_config_7 | 0x50000078 | 0x00000000 | |

| gpmc_config_7 | 0x50000078 | 0x00000F40 | |

so that it wil mapped to 16 MB of processor memory from start address 0x0. perfomed read operation but there is no activity.

Steps that we are performing are:

1. Configuring CM_L3MAIN1_GPMC_CLKCTRL 0x4A008728 to 0x0001

2. Configuring PIMUX as above mentioned table

3. Reseting the GPMC by setting GPMC_SYSCONFIG = 1

4. Waiting for the reset done by monitoring GPMC_SYSSTATUS

5. Configuring SYSCONFIG,IRQENABLE,TIMEOUR_CONTROL.,etc registers

6. Disable the CS in GPMC_SYSCONFIG_7

7. Configuring GPMC_CONFIG[1:7] registers

8. Enabling GPMC CS

pls confirm where we're doing wrong or missing something which needs to be taken care.

Regards,

Sarath