Hi, TI expert

Background of the question:

1) Our radar uses GPIO+DMA scheme, which runs in mcu3-0. The radar will always be in working state after starting up, and send the collected data to A72 through IPC;

2) Our parking application and algorithm runs in A72. In parking mode, it continuously processes radar data. In non-parking mode, data is received but not processed.

Question:

In non-parking mode, the radar works normally. In parking mode, the following problems may exist:

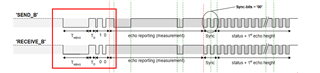

When mcu3-0 uses GPIO to generate command waveform, the actual measured low level time or high level time of hardware waveform is longer than that set by the software. For example, the low level time set by the software is 200us, but the actual measured waveform time is 215us.

This would cause the radar to be unable to parse the command waveform, thus not sending radar data to the MCU3-0.

The above questions are only available in parking mode. We would like to know:

1. Will the high load of A72 affect the operation of MCU3-0?

2. Will A72 and MCU preempt software resources or hardware resources?

The above problem is urgent, please help to analyze, thank you ~!