Hi,

We have below issue for the AM625X design:

1. Please advise the max. operating rate for GPMC;

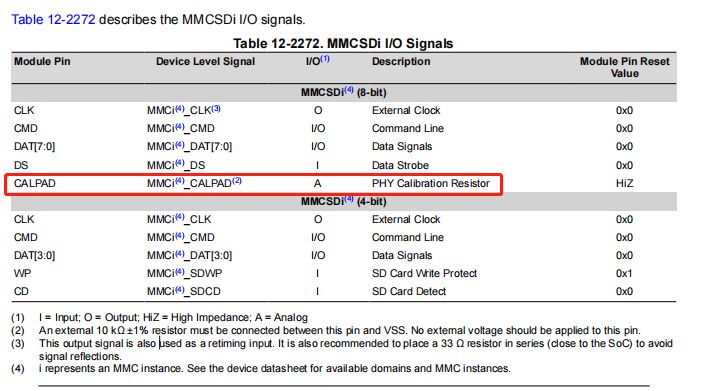

2. Please avise the location for the PHY Caibration resistor in the design, we can't find it in the design;

3. Please advise if the SOC communicate to SOC with the RGMI;

4. Please advise how to use the LVDS to 2 channels, we consider to use the Lane1&2 to LVDS#1 and Lane3&4 to LVDS#2.