Part Number: TMS320C6678

Hi team,

Here're few questions from the customer may need your help:

1)

https://e2echina.ti.com/cfs-file/__key/communityserver-discussions-components-files/120/zhca575.pdf

https://e2echina.ti.com/cfs-file/__key/communityserver-discussions-components-files/120/sprugh7.pdf

As can be seen from the above document, external memory can be read and written differently depending on whether or not L2cache is on and the size of it is on. When you turn on L2cache, the speed is slower from L2 to the external ram and faster from the external ram to L2. What is the main reason for the speed difference?

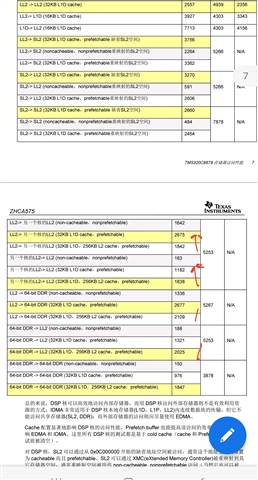

From the table 3 of zhca575 doc, CPU access memory: LL2<-->Other CoreL2,LL2<-->DDR3. The following table shows that when the CPU core accesses memory LL2->> external storage, the speed is reduced when L2 cache transfers are enabled.

| transmission | 32KBL1D,prefetchable | 256KB L2,32KB L1D,prefetchable |

| LL2->>OtherLL2 | 2675 | 1842 |

| OtherLL2->>LL2 | 1182 | 1838 |

| LL2->>DDR3 | 2677 | 2109 |

| DDR3->>LL2 | 1321 | 2025 |

2) According to the zhca575 doc, from Figure 2, Figure 4, it is clear that STDW has less latency to access memory than LDDW, which should not be related to cache.

According to the LDW, STW and other related instructions in the sprugh7 doc, LDW-like instructions have to go through multiple cycles to move the contents of the memory to the internal register. What is the reason for this design of c66x? If the LDW's memory is L1RAM, 1 cycle should be able to complete the data movement.

3) The L2 of each core can be read and written through the global address as tested in the zhaca575 doc. Unbooted cores can be used as boot core external RAM with lower access performance than SL2.

If cache size is dynamically sized in the program, will the data originally allocated in ram or cache be lost?

For example, in the following scenario:

A. The global variable x is allocated at L2, the program runs with L2 cache size adjusted up, and the address of the global variable x is within the scope of the cache adjustment. What happens when the variable x encounters cache inv, cache WB, and so on?

B. In the platform, configure the lL2 cache size to 32K, the remaining L2 as data memory, and adjust the L2 cache size to 0K when the program is running. Will local variables be placed in RAM that L2 is empty? Can the empty ram be used dynamically only as Heapmem, HeapBuf, etc.?

Could you help check this case? Thanks.

Best Regards,

Cherry