Other Parts Discussed in Thread: OMAPL138

Hi experts

Customers need to switch from the security version of AM3352 to the GP version of AM3352, they need the product to have two modes: normal boot mode (11001) and debug1 boot mode (00101)

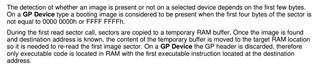

Originally on the safe CPU, they have no problem booting with the two methods,However, after changing the GP version, with debug1 mode (realized through an external hardware control switch), they did not connect UART0 and XIP devices, their products could not reach the third boot sequence SPI0, which is the mode they need.

But if the hardware is changed to debug2-00010b, it can automatically go to SPI0 sequence after uart0.

|

SYSBOOT[4:0] |

Boot Mode |

Use Case |

|

11001b |

SPI0,MMC0,EMAC1,UART0 |

Normal Boot |

|

00101b |

UART0,XIP,SPI0,NANDI2C |

Debug1 |

|

00010b |

UART0,SPI0,NAND,NANDI2C |

Debug2 |

They use GPMC connect to NAND flash, and use as bootloader. I saw this description in TRM.

But even if they clear the data of the first block of NAND flash, the boot still cannot start.

How to skip XIP boot? What is the difference between the HS version and the GP version in boot?

BR

Ethan