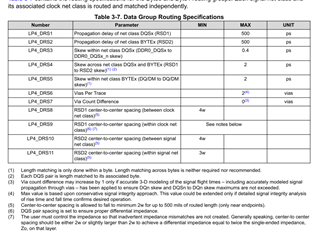

in the SPRAD06 documentation , table 3-7 listed the Data Group Routing Specification.

My query is : LPDDR4 may support the write level function between DQS and DQ, Why the skew limitation need control to max 2p?

The spec from Samsung LPDDR4 spec also mentioned the length matching, the margin is 240mil which may equal to 42ps (stripline), why Sitara side spec so restrict?

BR Jingcheng