Part Number: TDA4VM

Dear expert,

I try to boot A72 by boot_app in MCU10 and succesfully load atf_optee.appimage. But it failed at the next step.

NOTICE: BL31: v2.7(release):v2.7.0-359-g1309c6c805-dirty

NOTICE: BL31: Built : 07:46:16, Dec 18 2022

I/TC:

I/TC: OP-TEE version: 3.19.0 (gcc version 9.2.1 20191025 (GNU Toolchain for the A-profile Architecture 9.2-2019.12 (arm-9.10))) #1 Sun Dec 18 07:46:21 UTC 2022 aarch64

I/TC: WARNING: This OP-TEE configuration might be insecure!

I/TC: WARNING: Please check optee.readthedocs.io/.../porting_guidelines.html

I/TC: Primary CPU initializing

I/TC: SYSFW ABI: 3.1 (firmware rev 0x0008 '8.5.2--v08.05.02 (Chill Capybar')

I/TC: HUK Initialized

I/TC: Activated SA2UL device

I/TC: Fixing SA2UL firewall owner for GP device

I/TC: Enabled firewalls for SA2UL TRNG device

I/TC: SA2UL TRNG initialized

I/TC: SA2UL Drivers initialized

I/TC: Primary CPU switching to normal world boot

U-Boot SPL 2021.01-g7996ed51f1 (Dec 18 2022 - 07:46:35 +0000)

Model: Texas Instruments K3 J721E SoC

EEPROM not available at 0x50, trying to read at 0x51

Reading on-board EEPROM at 0x51 failed 1

Board: J721EX-PM1-SOM rev E2

SYSFW ABI: 3.1 (firmware rev 0x0008 '8.5.2--v08.05.02 (Chill Capybar')

EEPROM not available at 0x50, trying to read at 0x51

Reading on-board EEPROM at 0x51 failed 1

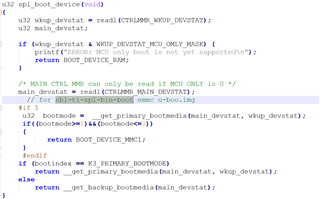

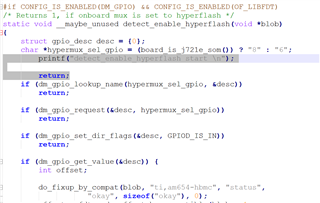

Trying to boot from SPI

cadence_spi spi@47040000: Can't get reset: -2

jedec_spi_nor flash@0: unrecognized JEDEC id bytes: 2c, 5b, 1b

SPI probe failed.

SPL: failed to boot from all boot devices

### ERROR ### Please RESET the board ###

All the image is from ti-processor-sdk-linux-j7-evm-08_05_00_08\board-support\prebuilt-images. And I place the atf_optee.appimage and u-boot-spl.appimage in the ospiflash. could you help me?