Hi,

I'm currently facing issues with Opengl rendering when we migrate our code from rtos SDK 8.2 to rtos SDK 8.5. Our code is based on the mosaic app from vision-apps. We are using the R5F node for the display and the opengl work is done through an openvx node on the A72.

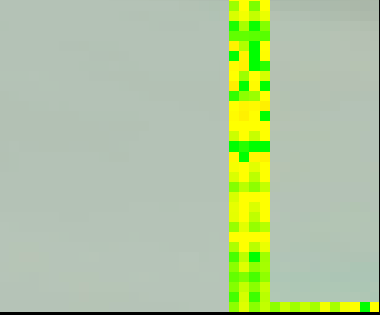

Below is the artifact we can see when running our code on a system running the SDK 8.5. This doesn't show up when running with the SDK Note that the line data changes from time to time, so it seem to be an uninitialised section.

Is there any known issue in the SDK that could cause this kind of issue? Also the boot log shows an error while reserving cma. Could this be one of the cause?

-----------------Section of dmesg-----------------

[ 0.000000] On node 0 totalpages: 1048576

[ 0.000000] DMA zone: 8192 pages used for memmap

[ 0.000000] DMA zone: 0 pages reserved

[ 0.000000] DMA zone: 524288 pages, LIFO batch:63

[ 0.000000] Normal zone: 8192 pages used for memmap

[ 0.000000] Normal zone: 524288 pages, LIFO batch:63

[ 0.000000] cma: Failed to reserve 400 MiB

---------------------------------------------------------

Best regards,