Hi experts:

The boot mode is SBL, booting from the SD card. Sdk is 8.2.

1.We hope to optimize the address loaded by the sections of SBL in the linker.cmd file to reserve more OCMC (ie MCU_MSRAM0) memory space for mcu1_0.

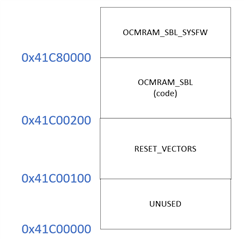

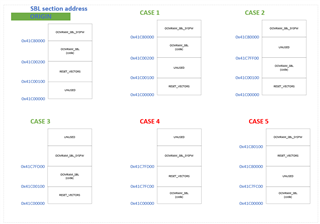

The default section allocation address in the SDK is as follows:

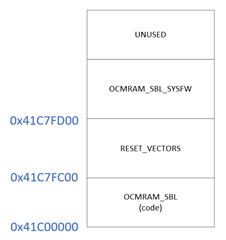

The section allocation address we want is as follows:

As shown in the figure above, after SBL starts and loads DMSC successfully, we want to assign the memory address starting from 0x41C7FC00 to mcu1_0.

2.Currently we have tried modifying the section address schemes listed below:

According to the above schemes, modify the linker.cmd file and compile it into sbl boot firmware (tiboot3.bin). Make SD card boot firmware.

The case 1, case 2 and case 3 can boot successfully. But the case 4 and case 5 boot failed.

3.We found that ’RESET_VECTORS‘ must be placed before ‘OCMRAM_SBL’, so that the SBL firmware can start normally.

And the case 4 can't be achieved.

4.Is it possible to use case 4 to start sbl?

Or other solutions?

Please help us resolve this issue, thanks.

linker.cmd:

/*----------------------------------------------------------------------------*/

/* File: linker.cmd */

/* Description: */

/* Link command file for Maxwell SBL */

/* */

/* Platform: R5 Cores on AM65xx */

/* (c) Texas Instruments 2018, All rights reserved. */

/*----------------------------------------------------------------------------*/

--retain="*(.bootCode)"

--retain="*(.startupCode)"

--retain="*(.startupData)"

--retain="*(.intvecs)"

--retain="*(.intc_text)"

--retain="*(.rstvectors)"

--retain="*(.irqStack)"

--retain="*(.fiqStack)"

--retain="*(.abortStack)"

--retain="*(.undStack)"

--retain="*(.svcStack)"

--fill_value=0

--stack_size=0x2000

--heap_size=0x2000

--entry_point=_sblResetVectors /* SBL entry in SBL_init.asm */

-stack 0x2000 /* SOFTWARE STACK SIZE */

-heap 0x2000 /* HEAP AREA SIZE */

/* Stack Sizes for various modes */

__IRQ_STACK_SIZE = 0x1000;

__FIQ_STACK_SIZE = 0x1000;

__ABORT_STACK_SIZE = 0x800;

__UND_STACK_SIZE = 0x800;

__SVC_STACK_SIZE = 0x2000;

/*----------------------------------------------------------------------------*/

/* Memory Map */

MEMORY

{

/* Reset Vectors base address(RESET_VECTORS) should be 64 bytes aligned */

RESET_VECTORS (X) : origin=0x41C00000 length=0x100

/* MCU0 memory used for SBL. Available to app for dynamic use ~160KB */

/* RBL uses 0x41CC0000 and beyond. SBL, at load cannot cross this */

OCMRAM_SBL (RWIX) : origin=0x41C00100 length=0x80000-0x500

/* Used by SBL at runtime to load SYSFW. Available to app for dynamic use

* Populate the SCISERVER Board configuration paramters at 0x41C80000

* after SYSFW is done.

* Location of all board configurations: 0x41c80040 after SYSFW is done.

*/

OCMRAM_SBL_SYSFW (RWIX) : origin=0x41C7FC00 length=0x40000

/* This is the maximum required by custom boot app. Do not use. */

OCMRAM_SBL_RESERVED_CUST_BOOT (RWIX) : origin=0x41CC0000 length=0x40000 - 0x500

/* X509 Header to be left behind by CCS Init for Sciserver to read */

OCMC_RAM_X509_HEADER (RWIX) : ORIGIN = 0x41cffb00 , LENGTH = 0x500

} /* end of MEMORY */

/*----------------------------------------------------------------------------*/

/* Section Configuration */

SECTIONS

{

/* 'intvecs' and 'intc_text' sections shall be placed within */

/* a range of +\- 16 MB */

.rstvectors : {} palign(8) > RESET_VECTORS

.bootCode : {} palign(8) > OCMRAM_SBL

.startupCode : {} palign(8) > OCMRAM_SBL

.startupData : {} palign(8) > OCMRAM_SBL, type = NOINIT

.sbl_profile_info : {} palign(8) > RESET_VECTORS (HIGH)

.text : {} palign(8) > OCMRAM_SBL

.rodata : {} palign(8) > OCMRAM_SBL

.const : {} palign(8) > OCMRAM_SBL

.const.devgroup.MCU_WAKEUP : {} align(4) > OCMRAM_SBL

.const.devgroup.MAIN : {} align(4) > OCMRAM_SBL

.const.devgroup.DMSC_INTERNAL : {} align(4) > OCMRAM_SBL

.cinit : {} palign(8) > OCMRAM_SBL

.pinit : {} palign(8) > OCMRAM_SBL

.boardcfg_data : {} palign(128) > OCMRAM_SBL

.data : {} palign(128) > OCMRAM_SBL

.bss : {} align(4) > OCMRAM_SBL

.bss.devgroup.MAIN : {} align(4) > OCMRAM_SBL

.bss.devgroup.MCU_WAKEUP : {} align(4) > OCMRAM_SBL

.bss.devgroup.DMSC_INTERNAL : {} align(4) > OCMRAM_SBL

.sysmem : {} > OCMRAM_SBL

.stack : {} align(4) > OCMRAM_SBL (HIGH)

.irqStack : {. = . + __IRQ_STACK_SIZE;} align(4) > OCMRAM_SBL (HIGH)

RUN_START(__IRQ_STACK_START)

RUN_END(__IRQ_STACK_END)

.fiqStack : {. = . + __FIQ_STACK_SIZE;} align(4) > OCMRAM_SBL (HIGH)

RUN_START(__FIQ_STACK_START)

RUN_END(__FIQ_STACK_END)

.abortStack : {. = . + __ABORT_STACK_SIZE;} align(4) > OCMRAM_SBL (HIGH)

RUN_START(__ABORT_STACK_START)

RUN_END(__ABORT_STACK_END)

.undStack : {. = . + __UND_STACK_SIZE;} align(4) > OCMRAM_SBL (HIGH)

RUN_START(__UND_STACK_START)

RUN_END(__UND_STACK_END)

.svcStac : {. = . + __SVC_STACK_SIZE;} align(4) > OCMRAM_SBL (HIGH)

RUN_START(__SVC_STACK_START)

RUN_END(__SVC_STACK_END)

.firmware : {} palign(8) > OCMRAM_SBL_SYSFW

} /* end of SECTIONS */

/*----------------------------------------------------------------------------*/

/* Misc linker settings */

/*-------------------------------- END ---------------------------------------*/