Hi team,

Here's an issue from the customer may need your help:

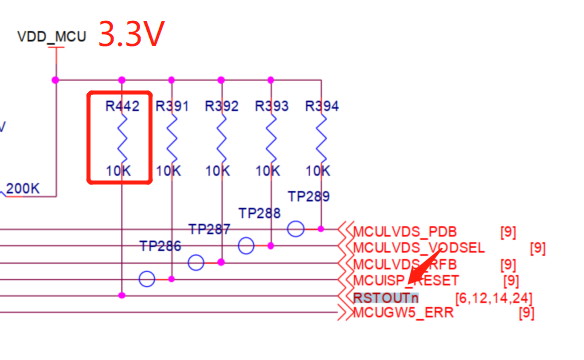

The RSTOUTN (F23 PIN) pin is still measured to be 3.3 V with both a pullup (3.3 V) and a pulldown applied externally.

So the customer would like to know what is the internal circuitry for this pin? When internally configured as a pull-up, does it not affect the level even if a pull-down resistor is added externally? And what structure does the internal pull-up look like? PMOS strong pull-up?

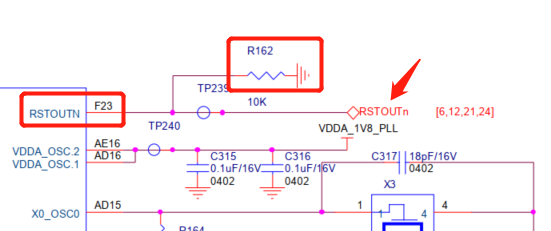

The following is the customer's schematic:

Could you help check this case? Thanks.

Best Regards,

Cherry