Hi Team,

Where can I find the schematic & layout guidance document of DM3730 ? We want to check the design for GPMC function.

Best Regards,

Madhurya

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Where can I find the schematic & layout guidance document of DM3730 ? We want to check the design for GPMC function.

Best Regards,

Madhurya

MadhuryaI was unable to find any guidelines specific to the DM3730 GPMC interface. However I did find the following that you may find useful.

In addition, there are some good details in the follwoing application note that you may also find helpful.

High-Speed Interface Layout Guidelines (Rev. J)

--Paul

Hi Paul!

Thanks for sharing this!

For our now-used CPU platform, there is not much guidance for the GPMC bus. Are there any other documents about GPMC BUS usage, I believe another platform is ok, just need more info here.

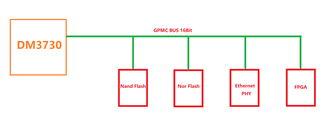

Below is the topology of our current design, for now, they want to know the GPMC BUS stub line length / the total length limit, the Parasitic capacitance requirements, which is critical for our design, the maximum number of peripheral devices that are supported.

Best Regards,

Madhurya

Hi Madhurya,

Sorry there is no such a document.

The datasheet shows that the timings apply with typical capacitive loading of 12pF - See Table 6-2. GPMC/NOR Flash Timing Conditions—Synchronous Mode

https://www.ti.com/lit/gpn/dm3730

For trace lengths, need to perform timing analysis. Perhaps the IBIS model could be used to simulate with the 4 loads and stubs. A 3D extraction of the board would provide best results. Clock buffering may be required like a 1 to 4 buffer.

Is this design using synchronous or asynch mode? How fast or slow does the system operate?

Regards,

Mark