Other Parts Discussed in Thread: TDA4VM

Hi Ti:

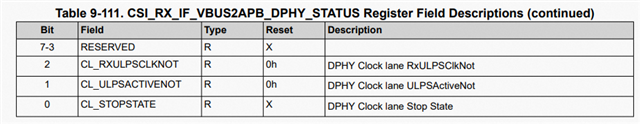

I connect camera to TDA4VM EVM. That is : camera-max9295——max9296-csi0 of J721E . The SDK I using is ti-processor-sdk-linux-j7-evm-08_05_00_08. After I set max9295 and max9296 I can get data from /dev/video0. The register CSI_RX_IF_VBUS2APB_DPHY_STATUS value toggle between 0x00222207 and 0x00333307. This means DPHY Clock is in Stop State ? So what should I do ? Thanks