Part Number: AM3357

Do you know it the TI AM3357BZCZA80 CPU can support serial MRAM for flash interface? We would like to use in a 1Gb size.

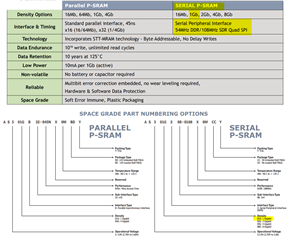

This is the device in question from Avalanche Technology:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AM3357

Do you know it the TI AM3357BZCZA80 CPU can support serial MRAM for flash interface? We would like to use in a 1Gb size.

This is the device in question from Avalanche Technology:

Hello Brad Caldwell

Thank you for the query.

Do you know it the TI AM3357BZCZA80 CPU can support serial MRAM for flash interface?

Can you please elaborate your query including what you meant by flash interface.

Is there a part number that you could share.

Regards,

Sreenivasa

Here's a link to the datasheet

Want to boot from it, I assume this would need to be SPI0 (CS0) SPI EEPROM boot mode with single data line

Hello Brad Caldwell

Thank you for sharing.

On a quick look i am assuming that the device might not be supported by the Am335x SPI bpoot

AM335x

26.1.8.6 SPI

26.1.8.6.1 Features

• Supports 12-MHz clock (50% duty cycle).

• Supports only SPI Mode 3 (clock polarity = 1, clock phase = 1).

• Supports only 24-bit addressable EEPROMs.

• Supports only 4-pin SPI mode (CS, CLK, Serial Input, Serial Output).

• The boot devices must be connected to chip select 0 and must support the read command (03h).

• The boot image is copied into internal memory and then executed.

Device

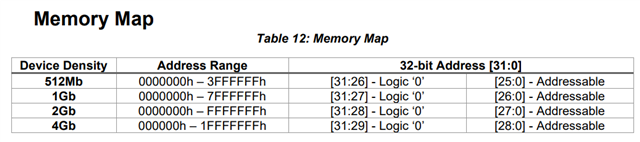

Memory Map Table 12: Memory Map

I need to consult the expert internally if you further need inputs. Let mw know your thoughts.

Regards,

Sreenivasa

I think your right. I saw the MRAM device expects a 32-bit address field for the read commands. Our ROM code only sends a 24-bit address field. That right there makes it incompatible for boot.

For normal runtime accesses, I don't see any issues, 4-wire SPI mode 3. With proper driver software, they should be able to create read/write commands. They would only be able to access one chip select at a time even though the MRAM is a dual die device. They would also have to manage the block protection signals using GPIOs.

Hello Brad Caldwell

Thank you for the inputs.

I will close the thread if you do not have additional inputs.

Regards,

Sreenivasa