Part Number: TDA4VM

Hello All,

I am trying to debug my code running into the TDA4VM board, the same at the moment is only using one of the cores on the MCU. The thing is that when I start the debugger the same for some reason get stucked on teh next address :

one thing I noticed ( because I'm using as a starting point for this script the one from the demo folders ) is that with the demo elf file run as expected the demo software, could be something related with the configuration I'm keeping from the demo on the cmm script?

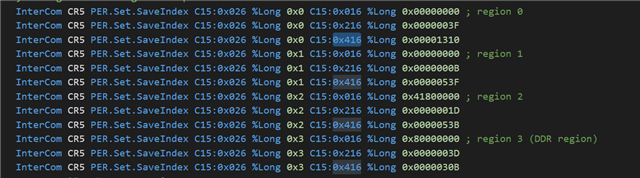

I notice that into the cmm script the next thing is being set:

Configuring in some way some memory regions, what are those C15 that are being set to some memory address, this should be configured according my map file for the memory address and starting points for my project?..

Where I can found information related to that? So far I was looking into the PDF's provided with the T32 installation but no handle to found any information related on how to configure/set those C15.

I'm not pretty sure this is the root source of my issues, but I think could be related.

One thing, this very same software I handle to debug using the Blackhawk prove, but now is intended to move to the Lauterbach ones.

Is anyone able to give me some advice/hint on this?..

Regards,

Ady