Hello Champs,

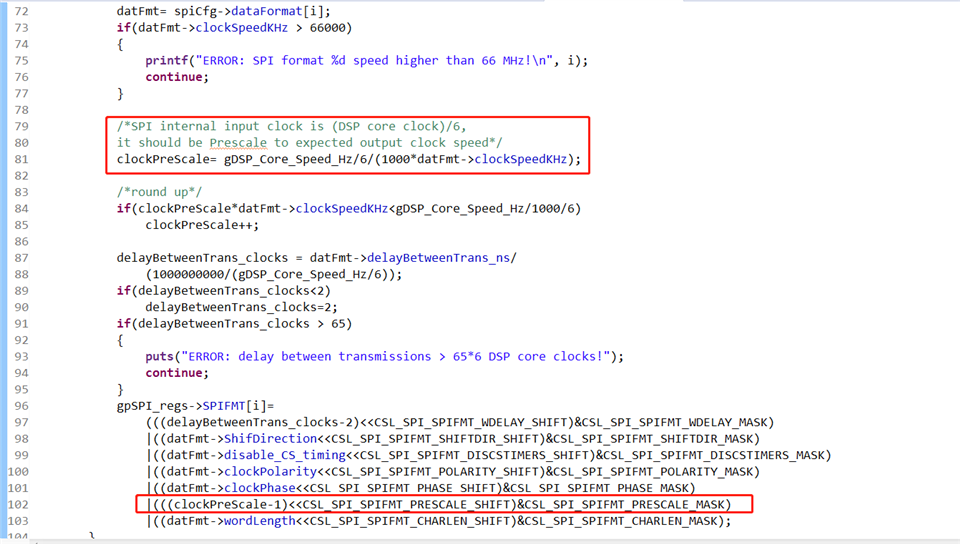

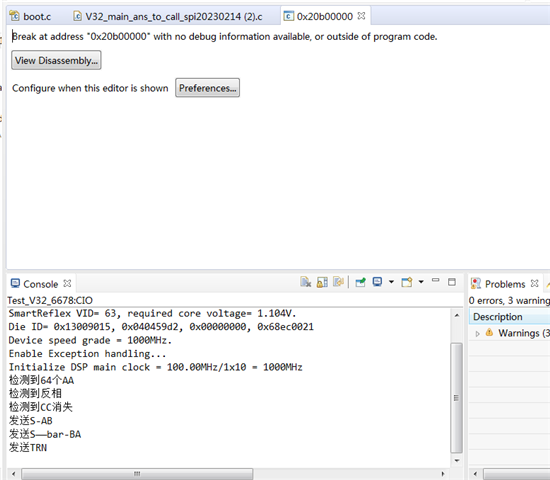

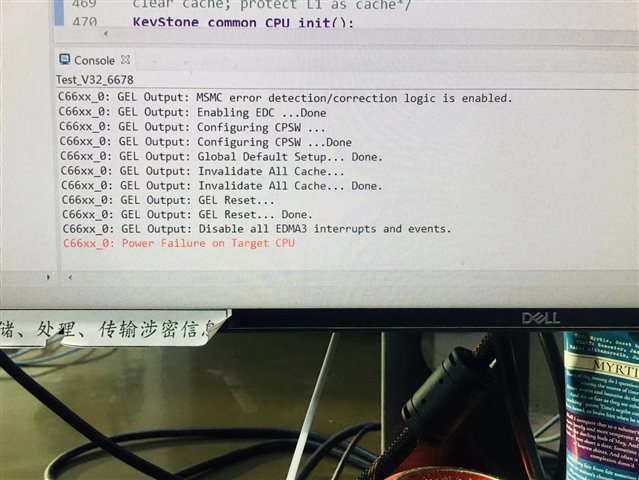

Customer uses the timer to control the SPI interface of C6678 to send data at a rate of 9.6k, send a 16bit data about every 104us, and receive a 16bit data at the same time. After receiving the data, it will do some processing on the data and generate the next data to be sent. The main frequency of the DSP is set to 1G, and the processing time must not exceed 104us. However, the program can run normally only when the SPI rate is configured to be above 60M, and the problem shown in the figure below will appear when the speed is less than 60M:

Or it prompted below error message when loading file.

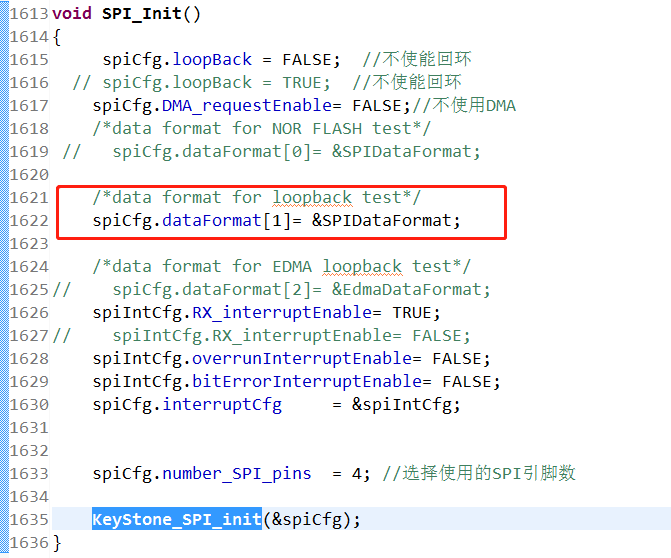

Below is the SPI configuration code

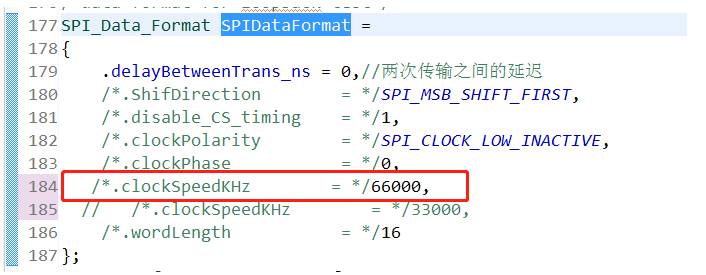

SPI_Data_Format SPIDataFormat =

{

.delayBetweenTrans_ns = 0,//两次传输之间的延迟

/*.ShifDirection = */SPI_MSB_SHIFT_FIRST,

/*.disable_CS_timing = */1,

/*.clockPolarity = */SPI_CLOCK_LOW_INACTIVE,

/*.clockPhase = */0,

// /*.clockSpeedKHz = */66000,

/*.clockSpeedKHz = */33000,

/*.wordLength = */16

};

SPI_Transfer_Param SPITransferParam =

{

SPI_CS_0, /*Chip select number*/

1, /*select one of the 4 SPI formats*/

SPI_CS_NO_HOLD, /*hold CS between multiple words*/

FALSE, /*Enable the delay counter at the end of the current transaction*/

// TRUE,

2 /*number of bytes per SPI word*/

};

Thanks

Regards

Shine