Hi

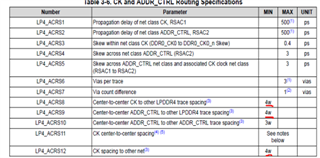

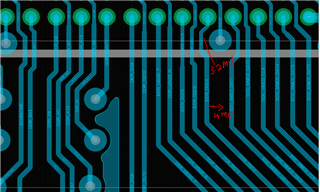

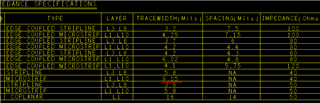

We would like to know regarding lpddr4 spacing requirements.As per TI recommendation its 4W except for certain cases where its 3W. However in AM62xx or AM64xx evaluation board only 3W spacing is followed for all signal spacing.Nowhere 4W is followed. Please let us know if 3W spacing is sufficient.