Other Parts Discussed in Thread: SN65DSI83

Hi,

we need to support second DSI (dsi1) interface on custom board built around j721s2 SoC om Linux.

Currently, we already have support for display attached to the primary DSI interface, that is dsi0.

Current working pipeline for dsi0 is:

dss vp2 -> cadence dsi0 + DSI_WRAP -> sn65dsi83 bridge -> LVDS panel

For secondary DSI interface, that is dsi1, the pipeline would be:

dss vp1 -> cadence dsi1 + DSI_WRAP -> lt8912b bridge -> HDMI connector

We have added missing device-tree definitions for dphy_tx1 and dsi1 peripherals in linux-ti like so:

From 727523ea6ce6c98192607c9db37ec41473a5559c Mon Sep 17 00:00:00 2001

From: Primoz Fiser <primoz.fiser@norik.com>

Date: Wed, 1 Mar 2023 15:15:40 +0100

Subject: [PATCH] arm64: dts: ti: k3-j721s2: rename dphy0 to dphy_tx0

Rename dphy0 to dphy_tx0 and follow the same naming convention as with

DPHY RX nodes. This then allows us to add additional DPHY TX node

similar as with k3-j721s4 SoC.

Signed-off-by: Primoz Fiser <primoz.fiser@norik.com>

---

arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi | 4 ++--

1 file changed, 2 insertions(+), 2 deletions(-)

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

index be0002f6be06..914671097917 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

@@ -1517,7 +1517,7 @@ dp0_ports: ports {

};

};

- dphy0: phy@4480000 {

+ dphy_tx0: phy@4480000 {

compatible = "ti,j721e-dphy";

reg = <0x0 0x04480000 0x0 0x1000>;

clocks = <&k3_clks 363 8>, <&k3_clks 363 14>;

@@ -1537,7 +1537,7 @@ dsi0: dsi@4800000 {

power-domains = <&k3_pds 154 TI_SCI_PD_EXCLUSIVE>;

interrupt-parent = <&gic500>;

interrupts = <GIC_SPI 600 IRQ_TYPE_LEVEL_HIGH>;

- phys = <&dphy0>;

+ phys = <&dphy_tx0>;

phy-names = "dphy";

dsi0_ports: ports {

--

2.25.1

From 8251ac9f497d8758cf771aa6f8a1f78feac322cd Mon Sep 17 00:00:00 2001

From: Primoz Fiser <primoz.fiser@norik.com>

Date: Wed, 1 Mar 2023 15:20:31 +0100

Subject: [PATCH] arm64: dts: ti: k3-j721s2: add dsi1 and dphy_tx1

Add nodes for secondary DSI port accompanied by DPHY TX found on

k3-j721s2 SoCs.

Signed-off-by: Primoz Fiser <primoz.fiser@norik.com>

---

arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi | 35 ++++++++++++++++++++++

1 file changed, 35 insertions(+)

diff --git a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

index 914671097917..c0a1896147e2 100644

--- a/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi

@@ -1529,6 +1529,18 @@ dphy_tx0: phy@4480000 {

assigned-clock-rates = <19200000>;

};

+ dphy_tx1: phy@4481000 {

+ compatible = "ti,j721e-dphy";

+ reg = <0x0 0x04481000 0x0 0x1000>;

+ clocks = <&k3_clks 364 8>, <&k3_clks 364 14>;

+ clock-names = "psm", "pll_ref";

+ #phy-cells = <0>;

+ power-domains = <&k3_pds 364 TI_SCI_PD_EXCLUSIVE>;

+ assigned-clocks = <&k3_clks 364 14>;

+ assigned-clock-parents = <&k3_clks 364 15>;

+ assigned-clock-rates = <19200000>;

+ };

+

dsi0: dsi@4800000 {

compatible = "ti,j721e-dsi";

reg = <0x0 0x04800000 0x0 0x100000>, <0x0 0x04710000 0x0 0x100>;

@@ -1552,6 +1564,29 @@ port@1 {

};

};

+ dsi1: dsi@4900000 {

+ compatible = "ti,j721e-dsi";

+ reg = <0x0 0x04900000 0x0 0x100000>, <0x0 0x04720000 0x0 0x100>;

+ clocks = <&k3_clks 155 4>, <&k3_clks 155 1>;

+ clock-names = "dsi_p_clk", "dsi_sys_clk";

+ power-domains = <&k3_pds 155 TI_SCI_PD_EXCLUSIVE>;

+ interrupt-parent = <&gic500>;

+ interrupts = <GIC_SPI 601 IRQ_TYPE_LEVEL_HIGH>;

+ phys = <&dphy_tx1>;

+ phy-names = "dphy";

+

+ dsi1_ports: ports {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ port@0 {

+ reg = <0>;

+ };

+ port@1 {

+ reg = <1>;

+ };

+ };

+ };

+

dss: dss@4a00000 {

compatible = "ti,j721e-dss";

reg =

--

2.25.1

And we can see drivers for entire pipeline probing successfully!

Here is output from modetest -M tidss:

# modetest -M tidss

Encoders:

id crtc type possible crtcs possible clones

38 37 none 0x00000001 0x00000001

47 46 none 0x00000002 0x00000002

Connectors:

id encoder status name size (mm) modes encoders

39 38 connected HDMI-A-1 520x320 17 38

modes:

index name refresh (Hz) hdisp hss hse htot vdisp vss vse vtot)

#0 1920x1080 60.00 1920 2008 2052 2200 1080 1084 1089 1125 148500 flags: phsync, pvsync; type: driver

#1 1920x1080 60.00 1920 2008 2052 2200 1080 1084 1089 1125 148500 flags: phsync, pvsync; type: driver

#2 1920x1080 59.94 1920 2008 2052 2200 1080 1084 1089 1125 148352 flags: phsync, pvsync; type: driver

#3 1920x1080 50.00 1920 2448 2492 2640 1080 1084 1089 1125 148500 flags: phsync, pvsync; type: driver

#4 1920x1080 50.00 1920 2448 2492 2640 1080 1084 1089 1125 148500 flags: phsync, pvsync; type: driver

#5 1920x1080 24.00 1920 2558 2602 2750 1080 1084 1089 1125 74250 flags: phsync, pvsync; type: driver

#6 1680x1050 59.88 1680 1728 1760 1840 1050 1053 1059 1080 119000 flags: phsync, nvsync; type: driver

#7 1600x900 60.00 1600 1624 1704 1800 900 901 904 1000 108000 flags: phsync, pvsync; type: driver

#8 1280x1024 60.02 1280 1328 1440 1688 1024 1025 1028 1066 108000 flags: phsync, pvsync; type: driver

#9 1440x900 59.90 1440 1488 1520 1600 900 903 909 926 88750 flags: phsync, nvsync; type: driver

#10 1280x800 59.91 1280 1328 1360 1440 800 803 809 823 71000 flags: phsync, nvsync; type: driver

#11 1280x720 60.00 1280 1390 1430 1650 720 725 730 750 74250 flags: phsync, pvsync; type: driver

#12 1280x720 60.00 1280 1390 1430 1650 720 725 730 750 74250 flags: phsync, pvsync; type: driver

#13 1280x720 50.00 1280 1720 1760 1980 720 725 730 750 74250 flags: phsync, pvsync; type: driver

#14 800x600 60.32 800 840 968 1056 600 601 605 628 40000 flags: phsync, pvsync; type: driver

#15 720x480 60.00 720 736 798 858 480 489 495 525 27027 flags: nhsync, nvsync; type: driver

#16 720x480 60.00 720 736 798 858 480 489 495 525 27027 flags: nhsync, nvsync; type: driver

props:

1 EDID:

flags: immutable blob

blobs:

value:

00ffffffffffff00220e863401010101

2b1e0103803420782a5595a9544c9e24

0d5054a54b00d1c081c0a9c0b3009500

81008180a940283c80a070b023403020

360006442100001a000000fd00184b1b

5e14000a202020202020000000fc0048

50205a32346e2047320a2020000000ff

0036434d3034333032534c0a2020019b

020324f150101f041303120211050706

14161520012309070767030c00100000

28e2002b023a801871382d40582c4500

06442100001e023a80d072382d40102c

458006442100001e011d007251d01e20

6e28550006442100001e283c80a070b0

23403020360006442100001aaf4b80a0

70b02b403020360006442100001a0033

2 DPMS:

flags: enum

enums: On=0 Standby=1 Suspend=2 Off=3

value: 0

5 link-status:

flags: enum

enums: Good=0 Bad=1

value: 0

6 non-desktop:

flags: immutable range

values: 0 1

value: 0

4 TILE:

flags: immutable blob

blobs:

value:

20 CRTC_ID:

flags: object

value: 37

48 47 connected LVDS-1 216x135 1 47

modes:

index name refresh (Hz) hdisp hss hse htot vdisp vss vse vtot)

#0 1280x800 59.07 1280 1380 1399 1440 800 804 808 823 70000 flags: nhsync, nvsync; type: preferred, driver

props:

1 EDID:

flags: immutable blob

blobs:

value:

2 DPMS:

flags: enum

enums: On=0 Standby=1 Suspend=2 Off=3

value: 0

5 link-status:

flags: enum

enums: Good=0 Bad=1

value: 0

6 non-desktop:

flags: immutable range

values: 0 1

value: 0

4 TILE:

flags: immutable blob

blobs:

value:

20 CRTC_ID:

flags: object

value: 46

CRTCs:

id fb pos size

37 61 (0,0) (1920x1080)

#0 1920x1080 60.00 1920 2008 2052 2200 1080 1084 1089 1125 148500 flags: phsync, pvsync; type: driver

props:

22 ACTIVE:

flags: range

values: 0 1

value: 1

23 MODE_ID:

flags: blob

blobs:

value:

144402008007d8070408980800003804

3c044104650400003c00000005000000

40000000313932307831303830000000

00000000000000000000000000000000

00000000

19 OUT_FENCE_PTR:

flags: range

values: 0 18446744073709551615

value: 0

24 VRR_ENABLED:

flags: range

values: 0 1

value: 0

27 CTM:

flags: blob

blobs:

value:

28 GAMMA_LUT:

flags: blob

blobs:

value:

29 GAMMA_LUT_SIZE:

flags: immutable range

values: 0 4294967295

value: 256

46 61 (0,0) (1280x800)

#0 1280x800 59.07 1280 1380 1399 1440 800 804 808 823 70000 flags: nhsync, nvsync; type: preferred, driver

props:

22 ACTIVE:

flags: range

values: 0 1

value: 1

23 MODE_ID:

flags: blob

blobs:

value:

70110100000564057705a00500002003

24032803370300003b0000000a000000

48000000313238307838303000000000

00000000000000000000000000000000

00000000

19 OUT_FENCE_PTR:

flags: range

values: 0 18446744073709551615

value: 0

24 VRR_ENABLED:

flags: range

values: 0 1

value: 0

27 CTM:

flags: blob

blobs:

value:

28 GAMMA_LUT:

flags: blob

blobs:

value:

29 GAMMA_LUT_SIZE:

flags: immutable range

values: 0 4294967295

value: 256

Planes:

id crtc fb CRTC x,y x,y gamma size possible crtcs

31 37 61 0,0 0,0 0 0x00000003

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 1

17 FB_ID:

flags: object

value: 61

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 37

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 1920

16 CRTC_H:

flags: range

values: 0 2147483647

value: 1080

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 125829120

12 SRC_H:

flags: range

values: 0 4294967295

value: 70778880

32 zpos:

flags: range

values: 0 3

value: 0

33 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

34 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

35 alpha:

flags: range

values: 0 65535

value: 65535

36 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

40 46 61 0,0 0,0 0 0x00000003

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 1

17 FB_ID:

flags: object

value: 61

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 46

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 1280

16 CRTC_H:

flags: range

values: 0 2147483647

value: 800

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 83886080

12 SRC_H:

flags: range

values: 0 4294967295

value: 52428800

41 zpos:

flags: range

values: 0 3

value: 0

42 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

43 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

44 alpha:

flags: range

values: 0 65535

value: 65535

45 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

49 0 0 0,0 0,0 0 0x00000003

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 0

17 FB_ID:

flags: object

value: 0

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 0

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 0

16 CRTC_H:

flags: range

values: 0 2147483647

value: 0

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 0

12 SRC_H:

flags: range

values: 0 4294967295

value: 0

50 zpos:

flags: range

values: 0 3

value: 0

51 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

52 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

53 alpha:

flags: range

values: 0 65535

value: 65535

54 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

55 0 0 0,0 0,0 0 0x00000003

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 0

17 FB_ID:

flags: object

value: 0

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 0

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 0

16 CRTC_H:

flags: range

values: 0 2147483647

value: 0

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 0

12 SRC_H:

flags: range

values: 0 4294967295

value: 0

56 zpos:

flags: range

values: 0 3

value: 0

57 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

58 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

59 alpha:

flags: range

values: 0 65535

value: 65535

60 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

Frame buffers:

id size pitch

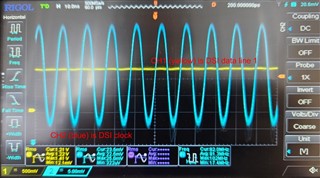

Now when we try to output something via HDMI/dsi1 (secondary dsi interface) we get nothing on DSI data lines (Channel 1 on oscilloscope):

# modetest -M tidss -s 39@37:720x480-60 setting mode 720x480-60.00Hz@XR24 on connectors 39, crtc 37

However DSI clock signal is OK (Channel 2 on oscilloscope) and changes depending on the selected mode:

We simply don't know why data lines are not getting any data?

Here is relevant DSS port configuration:

&dss {

/*

* These clock assignments are chosen to enable the following outputs:

*

* VP0 - DisplayPort SST

* VP1 - DPI0

* VP2 - DSI

*/

assigned-clocks = <&k3_clks 158 2>,

<&k3_clks 158 5>,

<&k3_clks 158 14>;

assigned-clock-parents = <&k3_clks 158 3>,

<&k3_clks 158 7>,

<&k3_clks 158 16>;

};

&dss_ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dpi0_out: endpoint {

remote-endpoint = <&dp0_in>;

};

};

/* TODO: Can DSS VP1 be used for DSI1 input? */

port@1 {

reg = <1>;

dpi1_out: endpoint {

remote-endpoint = <&dsi1_in>;

};

};

port@2 {

reg = <2>;

dpi2_out: endpoint {

remote-endpoint = <&dsi0_in>;

};

};

};

So the question can DSS's vp1 port be used to drive dsi1 input?

We are a bit puzzled by the following snippets in the drivers:

static void cdns_dsi_j721e_enable(struct cdns_dsi *dsi)

{

/*

* Enable DPI0 as its input. DSS0 DPI2 is connected

* to DSI DPI0. This is the only supported configuration on

* J721E.

*/

writel(DSI_WRAP_DPI_0_EN, dsi->j721e_regs + DSI_WRAP_DPI_CONTROL);

}

static void dispc_initial_config(struct dispc_device *dispc)

{

dispc_plane_init(dispc);

dispc_vp_init(dispc);

/* Note: Hardcoded DPI routing on J721E for now */

if (dispc->feat->subrev == DISPC_J721E) {

dispc_write(dispc, DISPC_CONNECTIONS,

FLD_VAL(2, 3, 0) | /* VP1 to DPI0 */

FLD_VAL(8, 7, 4) /* VP3 to DPI1 */

);

}

}

Thanks for ideas in advance!

BR,

Primoz