hi TI experts

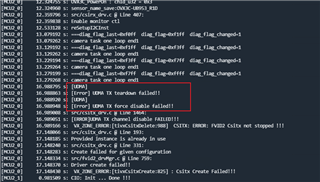

In the test, we found that there is a probability that CSI TX UDMA will fail. The specific log is as follows:

[MCU2_0] 0.979499 s: CIO: Init ... Done !!!

[MCU2_0] 0.979579 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz>

[MCU2_0] 0.979619 s: APP: Init ... !!!

[MCU2_0] 0.979641 s:

[MCU2_0] 0.979666 s: MCU2_0 VERSION INFO

[MCU2_0] 0.979711 s: =======================

[MCU2_0] 0.979751 s:

[MCU2_0] 0.979776 s: #BUILD DATE: 2023-02-28

[MCU2_0] 0.979815 s: #BUILD TIME: 11:11:48

[MCU2_0] 0.979846 s: #BUILD USER: jenkins@murg

[MCU2_0] 0.979878 s: #BUILD BRANCH: murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[MCU2_0] 0.979928 s: #BUILD PROFILE: release

[MCU2_0] 0.979959 s: #BUILD VERSION: R04d00

[MCU2_0] 0.979998 s:

[MCU2_0] 0.980019 s: =======================

[MCU2_0] 0.980052 s:

[MCU2_0] 0.980078 s: =======================

[MCU2_0] 0.980119 s: writing system info... base addr daff017c

[MCU2_0] 0.980177 s: date addr daff017c is 2023-02-28

[MCU2_0] 0.980286 s: time addr daff0188 is 11:11:48

[MCU2_0] 0.980385 s: project addr daff0194 is murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[MCU2_0] 0.980991 s: version addr daff01b4 is R04d00

[MCU2_0] 0.981122 s: done!

[MCU2_0] 0.981151 s: =======================

[MCU2_0] 0.981185 s: SCICLIENT: Init ... !!!

[MCU2_0] 1.070384 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[MCU2_0] 1.070424 s: SCICLIENT: DMSC FW revision 0x15

[MCU2_0] 1.070448 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_0] 1.070472 s: SCICLIENT: Init ... Done !!!

[MCU2_0] 1.070493 s: UDMA: Init ... !!!

[MCU2_0] 1.074160 s: UDMA: Init ... Done !!!

[MCU2_0] 1.074212 s: MEM: Init ... !!!

[MCU2_0] 1.074245 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e4000000 of size 16777216 bytes !!!

[MCU2_0] 1.074297 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 3600000 of size 131072 bytes !!!

[MCU2_0] 1.074359 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000000) @ db000000 of size 16777216 bytes !!!

[MCU2_0] 1.074400 s: MEM: Init ... Done !!!

[MCU2_0] 1.074418 s: IPC: Init ... !!!

[MCU2_0] 1.074444 s: IPC: 8 CPUs participating in IPC !!!

[MCU2_0] 1.085515 s: IPC: Init ... Done !!!

[MCU2_0] 1.085574 s: APP: Temp skip syncing with 7 CPUs ... !!!

[MCU2_0] 1.085683 s: REMOTE_SERVICE: Init ... !!!

[MCU2_0] 1.087183 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_0] 1.087245 s: APP_INIT: uCom_To_Ipc init Func Call... !!!

[MCU2_0] 1.087274 s: [uCom_To_Ipc_Init] ucom_to_ipc_self_cpu_id = 3 ... !!!

[MCU2_0] 1.087304 s: uCom_to_ipc: Init ... Start !!!

[MCU2_0] 1.087341 s: [uCom_To_Ipc_Init] num_cpus = 5 ... !!!

[MCU2_0] 1.087365 s: [uCom_To_Ipc_Init] self_cpu_id = 3 ... !!!

[MCU2_0] 1.087390 s: uCom to IPC: Init ... !!!

[MCU2_0] 1.087413 s: uCom to IPC: 5 CPUs participating in IPC !!!

[MCU2_0] 1.088055 s: uCom to IPC: Init ... Done !!!

[MCU2_0] 1.088103 s: uCom_to_ipc: Init ... Done !!!

[MCU2_0] 1.088225 s: ETHFW: Init ... !!!

[MCU2_0] 1.089657 s: [Board_ethConfigCpsw9g] LINE 728 :Board_cpsw9gEthConfig[6]

[MCU2_0] 1.089734 s: [Board_ethConfigCpsw9g] LINE 728 :Board_cpsw9gEthConfig[7]

[MCU2_0] 1.089907 s: [EnetBoard_initEthFw] LINE 258 :disable EnetAppUtils_enableClkOut

[MCU2_0] 1.090245 s: uCom to IPC: register notify handler.

[MCU2_0] 1.090341 s: HIL flag = 0xaa,mode = 0x0

[MCU2_0] 1.107892 s: CPSW_9G Test on MAIN NAVSS

[MCU2_0] 1.120859 s: [EnetBoard_setPhyConfigRmii] LINE 500 :config RMII,skipExtendedCfg should not be skipped

[MCU2_0] 1.120966 s: [EthFw_initLinkArgs] LINE 543 :EnetBoard_setPhyConfig done macport = 6 phyaddr = 0

[MCU2_0] 1.121040 s: [EthFw_initLinkArgs] LINE 554 :force set linkCfg ENET_SPEED_100MBIT & ENET_DUPLEX_FULL

[MCU2_0] 1.121269 s: [EnetPhy_open] LINE 317 : EnetPhy_isAlive = 1

[MCU2_0] 1.121340 s: [EnetPhy_initState] hPhy->phyCfg.isStrapped = 0

[MCU2_0] 1.121521 s: EnetPhy_bindDriver: PHY 0: OUI:006037 Model:10 Ver:02 <-> 'tja1101b_phy' : OK

[MCU2_0] 1.121584 s: [EnetPhy_open] LINE 331 : EnetPhy_bindDriver = 0

[MCU2_0] 1.121637 s: [EnetPhy_open] LINE 344 : speed = 1 duplexity = 1

[MCU2_0] 1.121691 s: [EnetPhy_open] LINE 346 : EnetPhy_releaseHandle = 0

[MCU2_0] 1.121770 s: [EnetBoard_setPhyConfigRmii] LINE 514 :config RMII,skipExtendedCfg should not be skipped

[MCU2_0] 1.121846 s: [EthFw_initLinkArgs] LINE 543 :EnetBoard_setPhyConfig done macport = 7 phyaddr = -1

[MCU2_0] 1.121917 s: [EthFw_initLinkArgs] LINE 548 :force set linkCfg without Phy ENET_SPEED_100MBIT & ENET_DUPLEX_FULL

[MCU2_0] 1.122041 s: PHY 0 is alive

[MCU2_0] 1.126477 s: ETHFW: Version : 0.01.01

[MCU2_0] 1.126533 s: ETHFW: Build Date: Feb 28, 2023

[MCU2_0] 1.126560 s: ETHFW: Build Time: 10:41:17

[MCU2_0] 1.126581 s: ETHFW: Commit SHA: 970e3bd9

[MCU2_0] 1.126606 s: Set MAX_LEN to 1522

[MCU2_0] 1.126626 s: Set MAX_LEN to 1522 DONE!!

[MCU2_0] 1.126644 s: ETHFW: Init ... DONE !!!

[MCU2_0] 1.126662 s: ETHFW: Remote server Init ... !!!

[MCU2_0] 1.127854 s: Remote demo device (core : mcu2_0) .....

[MCU2_0] 1.127909 s: ETHFW: Remote server Init ... DONE !!!

[MCU2_0] 1.134773 s: Host MAC address: 70:ff:76:1d:92:c2

[MCU2_0] 1.177129 s: FVID2: Init ... !!!

[MCU2_0] 1.177240 s: FVID2: Init ... Done !!!

[MCU2_0] 1.177294 s: [xxx] mcu2_0 i2c init start

[MCU2_0] 1.177346 s: [maxim] init serializer 96717 start

[MCU2_0] 1.177384 s: DES_VDD1V1 & PDB UP!

[MCU2_0] 1.198548 s: [maxim] init serializer 96717 end

[MCU2_0] 1.198614 s: [xxx-DSS] appDssBt601DefaultSetDefaultPrm: set default timing

[MCU2_0] 1.198653 s: DSS: Init ... !!!

[MCU2_0] 1.198673 s: DSS: Display type is DPIIIIIIII !!!

[MCU2_0] 1.198696 s: [xxx-DSS] set nodeOverlayId = 6, nodeVpId = 10, nodeDpiId = 13, overlayId = 1, vpId = 1, IfWidth = 7

[MCU2_0] 1.198743 s: DSS: SoC init ... !!!

[MCU2_0] 1.198760 s: SCICLIENT: Sciclient_pmSetModuleState module=152 state=2

[MCU2_0] 1.199007 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.199037 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=4 parent=6

[MCU2_0] 1.199151 s: SCICLIENT: Sciclient_pmSetModuleClkParent success

[MCU2_0] 1.199186 s: SCICLIENT: Sciclient_pmSetModuleClkFreq module=152 clk=4 freq=96688800

[MCU2_0] 1.200447 s: SCICLIENT: Sciclient_pmSetModuleClkFreq success

[MCU2_0] 1.200476 s: SCICLIENT: Sciclient_pmModuleClkRequest module=152 clk=4 state=2 flag=0

[MCU2_0] 1.200776 s: SCICLIENT: Sciclient_pmModuleClkRequest success

[MCU2_0] 1.200801 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=13 parent=18

[MCU2_0] 1.200914 s: SCICLIENT: Sciclient_pmSetModuleClkParent success

[MCU2_0] 1.200939 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=9 parent=12

[MCU2_0] 1.201031 s: SCICLIENT: Sciclient_pmSetModuleClkParent success

[MCU2_0] 1.201054 s: [xxx-DSS] pll config: 4,6; 4,pixel; 13,18; 9,12;

[MCU2_0] 1.201078 s: DSS: SoC init ... Done !!!

[MCU2_0] 1.201131 s: [maxim] init serializer 96715 (8bit)start

[MCU2_0] 1.219287 s: [maxim] init serializer 96715 end

[MCU2_0] 1.219340 s: DSS: Board init ... !!!

[MCU2_0] 1.264140 s: DSS: Board init ... Done !!!

[MCU2_0] 1.264192 s: [xxx-DSS] force to set syncVp port available

[MCU2_0] 1.266084 s: [xxx-dss] appDctrlBt601DefaultInit start

[MCU2_0] 1.266312 s: [xxx-dss] appDctrlBt601DefaultInit: set discrete sync VP, id = 2

[MCU2_0] 1.266400 s: [xxx-dss] appDctrlBt601DefaultInit: set embedded data VP, id = 1

[MCU2_0] 1.266472 s: [xxx-dss] appDctrlBt601DefaultInit: set overlay params

[MCU2_0] 1.266520 s: [xxx-dss] appDctrlBt601DefaultInit: set layer params

[MCU2_0] 1.266561 s: DSS: Dss_ApplyResetSequence !!!

[MCU2_0] 1.286225 s: DSS: Init ... Done !!!

[MCU2_0] 1.286271 s: VHWA: VPAC Init ... !!!

[MCU2_0] 1.286292 s: SCICLIENT: Sciclient_pmSetModuleState module=290 state=2

[MCU2_0] 1.286467 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.286493 s: VHWA: LDC Init ... !!!

[MCU2_0] 1.290200 s: VHWA: LDC Init ... Done !!!

[MCU2_0] 1.290251 s: VHWA: MSC Init ... !!!

[MCU2_0] 1.301546 s: VHWA: MSC Init ... Done !!!

[MCU2_0] 1.301596 s: VHWA: NF Init ... !!!

[MCU2_0] 1.303258 s: VHWA: NF Init ... Done !!!

[MCU2_0] 1.303305 s: VHWA: VISS Init ... !!!

[MCU2_0] 1.311837 s: VHWA: VISS Init ... Done !!!

[MCU2_0] 1.311889 s: VHWA: VPAC Init ... Done !!!

[MCU2_0] 1.311925 s: VX_ZONE_INIT:Enabled

[MCU2_0] 1.311949 s: VX_ZONE_ERROR:Enabled

[MCU2_0] 1.311970 s: VX_ZONE_WARNING:Enabled

[MCU2_0] 1.313006 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target IPU1-0

[MCU2_0] 1.313321 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_NF

[MCU2_0] 1.313589 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_LDC1

[MCU2_0] 1.313835 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_MSC1

[MCU2_0] 1.314079 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_MSC2

[MCU2_0] 1.314423 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_VISS1

[MCU2_0] 1.314716 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE1

[MCU2_0] 1.314998 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE2

[MCU2_0] 1.315318 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DISPLAY1

[MCU2_0] 1.315610 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DISPLAY2

[MCU2_0] 1.315885 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CSITX

[MCU2_0] 1.316203 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE3

[MCU2_0] 1.316503 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE4

[MCU2_0] 1.316785 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE5

[MCU2_0] 1.317083 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE6

[MCU2_0] 1.317429 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE7

[MCU2_0] 1.317723 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE8

[MCU2_0] 1.317774 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[MCU2_0] 1.317802 s: APP: OpenVX Target kernel init ... !!!

[MCU2_0] 1.329342 s: APP: OpenVX Target kernel init ... Done !!!

[MCU2_0] 1.329393 s: CSI2RX: Init ... !!!

[MCU2_0] 1.329411 s: SCICLIENT: Sciclient_pmSetModuleState module=25 state=2

[MCU2_0] 1.329544 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.329573 s: SCICLIENT: Sciclient_pmSetModuleState module=26 state=2

[MCU2_0] 1.329720 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.329743 s: SCICLIENT: Sciclient_pmSetModuleState module=27 state=2

[MCU2_0] 1.330093 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.330150 s: SCICLIENT: Sciclient_pmSetModuleState module=147 state=2

[MCU2_0] 1.330272 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.330296 s: SCICLIENT: Sciclient_pmSetModuleState module=148 state=2

[MCU2_0] 1.330389 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.331140 s: CSI2RX: Init ... Done !!!

[MCU2_0] 1.331194 s: CSI2TX: Init ... !!!

[MCU2_0] 1.331216 s: SCICLIENT: Sciclient_pmSetModuleState module=25 state=2

[MCU2_0] 1.331310 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.331337 s: SCICLIENT: Sciclient_pmSetModuleState module=28 state=2

[MCU2_0] 1.331455 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.331478 s: SCICLIENT: Sciclient_pmSetModuleState module=296 state=2

[MCU2_0] 1.331577 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 1.332155 s: CSI2TX: Init ... Done !!!

[MCU2_0] 1.332199 s: ISS: Init ... !!!

[MCU2_0] 1.332231 s: IssSensor_Init ... Done !!!

[MCU2_0] 1.332303 s: vissRemoteServer_Init ... Done !!!

[MCU2_0] 1.332353 s: IttRemoteServer_Init ... Done !!!

[MCU2_0] 1.332378 s: UDMA Copy: Init ... !!!

[MCU2_0] 1.334150 s: UDMA Copy: Init ... Done !!!

[MCU2_0] 1.334208 s: APP: Init ... Done !!!

[MCU2_0] 1.334235 s: APP: Run ... !!!

[MCU2_0] 1.334255 s: IPC: Starting echo test ...

[MCU2_0] 1.340709 s: APP: Run ... Done !!!

[MCU2_0] 1.340873 s: ==================start init_diag_gpios()=============

[MCU2_0] 1.341986 s: MAX20087: SYS_CFG (20 ticks)

[MCU2_0] 1.343322 s: MAX20087_config end!!

[MCU2_0] 1.343499 s: MAX20087: VDD1V1 (0 ticks)

[MCU2_0] 1.344368 s: VDD1V1 UP had power on in max96717!

[MCU2_0] 1.344534 s: MAX20087: VIDEO1V8 (60 ticks)

[MCU2_0] 1.345339 s: VIDEO1V8 UP!

[MCU2_0] 1.345492 s: MAX20087: PDB9702 (60 ticks)

[MCU2_0] 1.349037 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[.] mcu3_0[x]

[MCU2_0] 1.349324 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[.] mcu3_0[x]

[MCU2_0] 1.349436 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[x]

[MCU2_0] 1.349531 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[x]

[MCU2_0] 1.356173 s: VDD 9702 PDB EN UP!

[MCU2_0] 1.356238 s: TDA4VM POC_EN UP!

[MCU2_0] 1.356285 s: MAX20087: I2C3 (5 ticks)

[MCU2_0] 1.357175 s: max20087 now init i2c3 9702 register

[MCU2_0] 1.441206 s: uComSendCamReSyncStatus send cam_re_sync_status =0

[MCU2_0] 1.457194 s: IssUb9702_953_init enter channel_mask=15 hilMode=0

[MCU2_0] 1.457313 s: [xxxx] in IssSensor_iAuto_Cfg start in raw mode 4

[MCU2_0] 1.486148 s: Function:CpswProxyServer_attachHandlerCb,HostId:0,CpswType:6

[MCU2_0] 1.486837 s: Function:CpswProxyServer_allocMacHandlerCb,HostId:0,Handle:9893e9fc,CoreKey:38acb7e6

[MCU2_0] 1.541205 s: uComSendCamReSyncStatus send cam_re_sync_status =0

[MCU2_0] 1.641206 s: uComSendCamReSyncStatus send cam_re_sync_status =0

[MCU2_0] 1.774993 s: Function:CpswProxyServer_allocTxHandlerCb,HostId:0,Handle:9893e9fc,CoreKey:38acb7e6

[MCU2_0] 1.779517 s: Function:CpswProxyServer_allocRxHandlerCb,HostId:0,Handle:9893e9fc,CoreKey:38acb7e6

[MCU2_0] 1.779822 s: Function:CpswProxyServer_ioctlHandlerCb,HostId:0,Handle:9893e9fc,CoreKey:38acb7e6, Cmd:1010401,InArgsLen:0, OutArgsLen:4

[MCU2_0] 1.798660 s: Function:CpswProxyServer_ioctlHandlerCb,HostId:0,Handle:9893e9fc,CoreKey:38acb7e6, Cmd:1010201,InArgsLen:24, OutArgsLen:4

[MCU2_0] 1.800504 s: Function:CpswProxyServer_registerMacHandlerCb,HostId:0,Handle:9893e9fc,CoreKey:38acb7e6, MacAddress:70:ff:76:1d:92:c1, FlowIdx:172, FlowIdxOffset:0

[MCU2_0] 1.800695 s: Cpsw_ioctlInternal: CPSW: Registered MAC address.ALE entry:16, Policer Entry:0

[MCU2_0] 1.801432 s: Function:CpswProxyServer_registerIpv4MacHandlerCb,HostId:0,Handle:9893e9fc,CoreKey:38acb7e6, MacAddress:70:ff:76:1d:92:c1 IPv4Addr:198.18.36.94

[MCU2_0] 1.801584 s: Failed to add Static ARP Entry

[MCU2_0] 1.801629 s:

[MCU2_0] ================LLI Table entries===========

[MCU2_0] 1.801657 s:

[MCU2_0] Number of Static ARP Entries: 0

[MCU2_0] 1.801678 s:

[MCU2_0] SNo. IP Address MAC Address

[MCU2_0] 1.801701 s: ------ ------------- ---------------

[MCU2_0] 1.801775 s: [CpswProxyServer_registerIpv4MacHandlerCb] LINE 1112 :force set RPMSG_KDRV_TP_ETHSWITCH_CMDSTATUS_OK

[MCU2_1] 0.981522 s: CIO: Init ... Done !!!

[MCU2_1] 0.982139 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz>

[MCU2_1] 0.982307 s: APP: Init ... !!!

[MCU2_1] 0.982405 s:

[MCU2_1] 0.982432 s: MCU2_1 VERSION INFO

[MCU2_1] 0.982474 s: =======================

[MCU2_1] 0.982507 s:

[MCU2_1] 0.982536 s: #BUILD DATE: 2023-02-28

[MCU2_1] 0.982569 s: #BUILD TIME: 11:11:48

[MCU2_1] 0.982597 s: #BUILD USER: jenkins@murg

[MCU2_1] 0.982631 s: #BUILD BRANCH: murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[MCU2_1] 0.982679 s: #BUILD PROFILE: release

[MCU2_1] 0.982715 s: #BUILD VERSION: R04d00

[MCU2_1] 0.982753 s:

[MCU2_1] 0.982772 s: =======================

[MCU2_1] 0.982802 s:

[MCU2_1] 0.982825 s: =======================

[MCU2_1] 0.982862 s: writing system info... base addr daff01c4

[MCU2_1] 0.982926 s: date addr daff01c4 is 2023-02-28

[MCU2_1] 0.982996 s: time addr daff01d0 is 11:11:48

[MCU2_1] 0.983082 s: project addr daff01dc is murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[MCU2_1] 0.983444 s: version addr daff01fc is R04d00

[MCU2_1] 0.983546 s: done!

[MCU2_1] 0.983571 s: =======================

[MCU2_1] 0.983617 s: SCICLIENT: Init ... !!!

[MCU2_1] 1.070693 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[MCU2_1] 1.070732 s: SCICLIENT: DMSC FW revision 0x15

[MCU2_1] 1.070756 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_1] 1.070778 s: SCICLIENT: Init ... Done !!!

[MCU2_1] 1.070798 s: UDMA: Init ... !!!

[MCU2_1] 1.075002 s: UDMA: Init ... Done !!!

[MCU2_1] 1.075054 s: MEM: Init ... !!!

[MCU2_1] 1.075086 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e5000000 of size 16777216 bytes !!!

[MCU2_1] 1.075166 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 3620000 of size 131072 bytes !!!

[MCU2_1] 1.075219 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000000) @ dc000000 of size 117440512 bytes !!!

[MCU2_1] 1.075267 s: MEM: Init ... Done !!!

[MCU2_1] 1.075288 s: IPC: Init ... !!!

[MCU2_1] 1.075316 s: IPC: 8 CPUs participating in IPC !!!

[MCU2_1] 1.085512 s: IPC: Init ... Done !!!

[MCU2_1] 1.085570 s: APP: Temp skip syncing with 7 CPUs ... !!!

[MCU2_1] 1.085667 s: REMOTE_SERVICE: Init ... !!!

[MCU2_1] 1.086965 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_1] 1.087021 s: APP_INIT: uCom_To_Ipc init Func Call... !!!

[MCU2_1] 1.087052 s: [uCom_To_Ipc_Init] ucom_to_ipc_self_cpu_id = 4 ... !!!

[MCU2_1] 1.087083 s: uCom_to_ipc: Init ... Start !!!

[MCU2_1] 1.087155 s: [uCom_To_Ipc_Init] num_cpus = 5 ... !!!

[MCU2_1] 1.087190 s: [uCom_To_Ipc_Init] self_cpu_id = 4 ... !!!

[MCU2_1] 1.087215 s: uCom to IPC: Init ... !!!

[MCU2_1] 1.087237 s: uCom to IPC: 5 CPUs participating in IPC !!!

[MCU2_1] 1.087820 s: uCom to IPC: Init ... Done !!!

[MCU2_1] 1.087859 s: uCom_to_ipc: Init ... Done !!!

[MCU2_1] 1.087884 s: FVID2: Init ... !!!

[MCU2_1] 1.087943 s: FVID2: Init ... Done !!!

[MCU2_1] 1.087984 s: [xxx] mcu2_0 i2c init start

[MCU2_1] 1.088011 s: VHWA: DMPAC: Init ... !!!

[MCU2_1] 1.088030 s: SCICLIENT: Sciclient_pmSetModuleState module=48 state=2

[MCU2_1] 1.088283 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 1.088325 s: SCICLIENT: Sciclient_pmSetModuleState module=305 state=2

[MCU2_1] 1.088534 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 1.088564 s: VHWA: DOF Init ... !!!

[MCU2_1] 1.100908 s: VHWA: DOF Init ... Done !!!

[MCU2_1] 1.100962 s: VHWA: SDE Init ... !!!

[MCU2_1] 1.103427 s: VHWA: SDE Init ... Done !!!

[MCU2_1] 1.103471 s: VHWA: DMPAC: Init ... Done !!!

[MCU2_1] 1.103496 s: VHWA: Codec: Init ... !!!

[MCU2_1] 1.103516 s: VHWA: VDEC Init ... !!!

[MCU2_1] 1.104360 s: uCom to IPC: register notify handler.

[MCU2_1] 1.104435 s: [SignalTransmain] delay 4s

[MCU2_1] 1.104482 s: [Localizationmain] delay 4s

[MCU2_1] 1.106858 s: [UssPerceptionmain] delay 4s

[MCU2_1] 1.116482 s: VHWA: VDEC Init ... Done !!!

[MCU2_1] 1.116533 s: VHWA: VENC Init ... !!!

[MCU2_1] 1.116761 s: MM_ENC_Init: No OCM RAM pool available, fallback to DDR mode for above mp params

[MCU2_1] 1.156746 s: VHWA: VENC Init ... Done !!!

[MCU2_1] 1.156797 s: VHWA: Init ... Done !!!

[MCU2_1] 1.156831 s: VX_ZONE_INIT:Enabled

[MCU2_1] 1.156856 s: VX_ZONE_ERROR:Enabled

[MCU2_1] 1.156876 s: VX_ZONE_WARNING:Enabled

[MCU2_1] 1.157845 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DMPAC_SDE

[MCU2_1] 1.158065 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DMPAC_DOF

[MCU2_1] 1.158329 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VDEC1

[MCU2_1] 1.158524 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VDEC2

[MCU2_1] 1.158710 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VENC1

[MCU2_1] 1.158894 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VENC2

[MCU2_1] 1.158939 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[MCU2_1] 1.158966 s: APP: OpenVX Target kernel init ... !!!

[MCU2_1] 1.159365 s: APP: OpenVX Target kernel init ... Done !!!

[MCU2_1] 1.159404 s: UDMA Copy: Init ... !!!

[MCU2_1] 1.161354 s: UDMA Copy: Init ... Done !!!

[MCU2_1] 1.161406 s: APP: Init ... Done !!!

[MCU2_1] 1.161431 s: APP: Run ... !!!

[MCU2_1] 1.161451 s: IPC: Starting echo test ...

[MCU2_1] 1.163857 s: APP: Run ... Done !!!

[MCU2_1] 1.167743 s:

[MCU2_1] 1.167801 s: spistatus: 0

[MCU2_1] 1.167826 s:

[MCU2_1] 1.167845 s: pinset: 0

[MCU2_1] 1.167876 s:

[MCU2_1] 1.167895 s: timerstatus: 0

[MCU2_1] 1.169238 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[x]

[MCU2_1] 1.169408 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[x]

[MCU2_1] 1.169494 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[x]

[MCU2_1] 1.349339 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[s] mcu3_0[x]

[C6x_1 ] 1.008995 s: CIO: Init ... Done !!!

[C6x_1 ] 1.009026 s: ### CPU Frequency <ORG = 1350000000 Hz>, <NEW = 1350000000 Hz>

[C6x_1 ] 1.009040 s: APP: Init ... !!!

[C6x_1 ] 1.009050 s:

[C6x_1 ] 1.009057 s: C6x_1 VERSION INFO

[C6x_1 ] 1.009065 s: =======================

[C6x_1 ] 1.009073 s:

[C6x_1 ] 1.009080 s: #BUILD DATE: 2023-02-28

[C6x_1 ] 1.009089 s: #BUILD TIME: 11:11:48

[C6x_1 ] 1.009097 s: #BUILD USER: jenkins@murg

[C6x_1 ] 1.009105 s: #BUILD BRANCH: murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[C6x_1 ] 1.009117 s: #BUILD PROFILE: release

[C6x_1 ] 1.009125 s: #BUILD VERSION: R04d00

[C6x_1 ] 1.009133 s:

[C6x_1 ] 1.009139 s: =======================

[C6x_1 ] 1.009148 s:

[C6x_1 ] 1.009155 s: =======================

[C6x_1 ] 1.009163 s: writing system info... base addr daff029c

[C6x_1 ] 1.009173 s: date addr daff029c is 2023-02-28

[C6x_1 ] 1.009189 s: time addr daff02a8 is 11:11:48

[C6x_1 ] 1.009205 s: project addr daff02b4 is murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[C6x_1 ] 1.009245 s: version addr daff02d4 is R04d00

[C6x_1 ] 1.009259 s: done!

[C6x_1 ] 1.009266 s: =======================

[C6x_1 ] 1.009274 s: SCICLIENT: Init ... !!!

[C6x_1 ] 1.070462 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[C6x_1 ] 1.070473 s: SCICLIENT: DMSC FW revision 0x15

[C6x_1 ] 1.070484 s: SCICLIENT: DMSC FW ABI revision 3.1

[C6x_1 ] 1.070494 s: SCICLIENT: Init ... Done !!!

[C6x_1 ] 1.070504 s: UDMA: Init ... !!!

[C6x_1 ] 1.075311 s: UDMA: Init ... Done !!!

[C6x_1 ] 1.075332 s: MEM: Init ... !!!

[C6x_1 ] 1.075345 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e7000000 of size 16777216 bytes !!!

[C6x_1 ] 1.075363 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!!

[C6x_1 ] 1.075379 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ e8000000 of size 50331648 bytes !!!

[C6x_1 ] 1.075395 s: MEM: Init ... Done !!!

[C6x_1 ] 1.075404 s: IPC: Init ... !!!

[C6x_1 ] 1.075418 s: IPC: 8 CPUs participating in IPC !!!

[C6x_1 ] 1.085516 s: IPC: Init ... Done !!!

[C6x_1 ] 1.085544 s: APP: Temp skip syncing with 7 CPUs ... !!!

[C6x_1 ] 1.085556 s: REMOTE_SERVICE: Init ... !!!

[C6x_1 ] 1.086100 s: REMOTE_SERVICE: Init ... Done !!!

[C6x_1 ] 1.086129 s: APP_INIT: uCom_To_Ipc init Func Call... !!!

[C6x_1 ] 1.086155 s: [xxx] mcu2_0 i2c init start

[C6x_1 ] 1.086171 s: VX_ZONE_INIT:Enabled

[C6x_1 ] 1.086180 s: VX_ZONE_ERROR:Enabled

[C6x_1 ] 1.086189 s: VX_ZONE_WARNING:Enabled

[C6x_1 ] 1.086913 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[C6x_1 ] 1.086930 s: APP: OpenVX Target kernel init ... !!!

[C6x_1 ] 1.087344 s: APP: OpenVX Target kernel init ... Done !!!

[C6x_1 ] 1.087360 s: UDMA Copy: Init ... !!!

[C6x_1 ] 1.089332 s: UDMA Copy: Init ... Done !!!

[C6x_1 ] 1.089357 s: APP: Init ... Done !!!

[C6x_1 ] 1.090051 s: APP: Run ... !!!

[C6x_1 ] 1.090062 s: IPC: Starting echo test ...

[C6x_1 ] 1.091338 s: APP: Run ... Done !!!

[C6x_1 ] 1.091644 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] C66X_1[s] C66X_2[x] C7X_1[P]

[C6x_1 ] 1.098491 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_1 ] 1.168978 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[x] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_1 ] 1.347984 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[x] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_2 ] 1.009154 s: CIO: Init ... Done !!!

[C6x_2 ] 1.009185 s: ### CPU Frequency <ORG = 1350000000 Hz>, <NEW = 1350000000 Hz>

[C6x_2 ] 1.009200 s: APP: Init ... !!!

[C6x_2 ] 1.009209 s:

[C6x_2 ] 1.009215 s: C6x_2 VERSION INFO

[C6x_2 ] 1.009223 s: =======================

[C6x_2 ] 1.009231 s:

[C6x_2 ] 1.009238 s: #BUILD DATE: 2023-02-28

[C6x_2 ] 1.009246 s: #BUILD TIME: 11:11:48

[C6x_2 ] 1.009255 s: #BUILD USER: jenkins@murg

[C6x_2 ] 1.009263 s: #BUILD BRANCH: murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[C6x_2 ] 1.009274 s: #BUILD PROFILE: release

[C6x_2 ] 1.009283 s: #BUILD VERSION: R04d00

[C6x_2 ] 1.009291 s:

[C6x_2 ] 1.009297 s: =======================

[C6x_2 ] 1.009305 s:

[C6x_2 ] 1.009312 s: =======================

[C6x_2 ] 1.009320 s: writing system info... base addr daff02e4

[C6x_2 ] 1.009330 s: date addr daff02e4 is 2023-02-28

[C6x_2 ] 1.009346 s: time addr daff02f0 is 11:11:48

[C6x_2 ] 1.009360 s: project addr daff02fc is murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[C6x_2 ] 1.009396 s: version addr daff031c is R04d00

[C6x_2 ] 1.009409 s: done!

[C6x_2 ] 1.009416 s: =======================

[C6x_2 ] 1.009424 s: SCICLIENT: Init ... !!!

[C6x_2 ] 1.070538 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[C6x_2 ] 1.070549 s: SCICLIENT: DMSC FW revision 0x15

[C6x_2 ] 1.070558 s: SCICLIENT: DMSC FW ABI revision 3.1

[C6x_2 ] 1.070568 s: SCICLIENT: Init ... Done !!!

[C6x_2 ] 1.070577 s: UDMA: Init ... !!!

[C6x_2 ] 1.075651 s: UDMA: Init ... Done !!!

[C6x_2 ] 1.075672 s: MEM: Init ... !!!

[C6x_2 ] 1.075685 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ eb000000 of size 16777216 bytes !!!

[C6x_2 ] 1.075703 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!!

[C6x_2 ] 1.075719 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ ec000000 of size 50331648 bytes !!!

[C6x_2 ] 1.075735 s: MEM: Init ... Done !!!

[C6x_2 ] 1.075744 s: IPC: Init ... !!!

[C6x_2 ] 1.075757 s: IPC: 8 CPUs participating in IPC !!!

[C6x_2 ] 1.088064 s: IPC: Init ... Done !!!

[C6x_2 ] 1.088094 s: APP: Temp skip syncing with 7 CPUs ... !!!

[C6x_2 ] 1.088106 s: REMOTE_SERVICE: Init ... !!!

[C6x_2 ] 1.088603 s: REMOTE_SERVICE: Init ... Done !!!

[C6x_2 ] 1.088631 s: APP_INIT: uCom_To_Ipc init Func Call... !!!

[C6x_2 ] 1.088655 s: [xxx] mcu2_0 i2c init start

[C6x_2 ] 1.088671 s: VX_ZONE_INIT:Enabled

[C6x_2 ] 1.088682 s: VX_ZONE_ERROR:Enabled

[C6x_2 ] 1.088692 s: VX_ZONE_WARNING:Enabled

[C6x_2 ] 1.089375 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[C6x_2 ] 1.089392 s: APP: OpenVX Target kernel init ... !!!

[C6x_2 ] 1.089753 s: APP: OpenVX Target kernel init ... Done !!!

[C6x_2 ] 1.089769 s: UDMA Copy: Init ... !!!

[C6x_2 ] 1.092314 s: UDMA Copy: Init ... Done !!!

[C6x_2 ] 1.092337 s: APP: Init ... Done !!!

[C6x_2 ] 1.096813 s: APP: Run ... !!!

[C6x_2 ] 1.096825 s: IPC: Starting echo test ...

[C6x_2 ] 1.098136 s: APP: Run ... Done !!!

[C6x_2 ] 1.098499 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] C66X_1[P] C66X_2[s] C7X_1[.]

[C6x_2 ] 1.098539 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] C66X_1[P] C66X_2[s] C7X_1[P]

[C6x_2 ] 1.168999 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[x] C66X_1[P] C66X_2[s] C7X_1[P]

[C6x_2 ] 1.348017 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[x] C66X_1[P] C66X_2[s] C7X_1[P]

[MCU2_0] 4.011204 s: OVX3C_Probe: chId_u32 = 0 SUCCESS!!!

[MCU2_0] 4.562211 s: OVX3C_Probe: chId_u32 = 1 SUCCESS!!!

[MCU2_0] 5.113230 s: OVX3C_Probe: chId_u32 = 2 SUCCESS!!!

[MCU2_0] 5.664224 s: OVX3C_Probe: chId_u32 = 3 SUCCESS!!!

[MCU2_0] 6.514884 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P]

[MCU2_0] 6.716252 s: sensor_name_save:OVX3C-UB953_R1D sensor_features_requested=0x158

[MCU2_0] 7.000018 s: [KK]OVX3C_Config: Read OVX3C Address=40 Register=0x100 regValue_u8=0

[MCU2_0] 7.000102 s: Configuring OVX3C imager 0x40.. Please wait till it finishes

[MCU2_0] 8.203047 s: [KK]OVX3C_Config: Read OVX3C Address=42 Register=0x100 regValue_u8=0

[MCU2_0] 8.203191 s: Configuring OVX3C imager 0x42.. Please wait till it finishes

[MCU2_0] 9.146734 s: KANKAN Software version = v2.82

[MCU2_0] 9.147185 s: OVX3C_PowerOn : chId_u32 = 0x0

[MCU2_0] 9.147242 s: OVX3C_PowerOn : chId_u32 = 0x1

[MCU2_0] 9.147284 s: OVX3C_PowerOn : chId_u32 = 0x2

[MCU2_0] 9.147321 s: OVX3C_PowerOn : chId_u32 = 0x3

[MCU2_0] 9.147496 s: sensor_name_save:OVX3C-UB953_R1D

[MCU2_0] 9.147547 s: i2c_init_ok = 2

[MCU2_0] 9.147580 s: waiting issUb9702_953_sensor init finsh

[MCU2_0] 9.406005 s: [KK]OVX3C_Config: Read OVX3C Address=44 Register=0x100 regValue_u8=0

[MCU2_0] 9.406086 s: Configuring OVX3C imager 0x44.. Please wait till it finishes

[MCU2_0] 10.147156 s: waiting issUb9702_953_sensor init finsh

[MCU2_0] 10.609028 s: [KK]OVX3C_Config: Read OVX3C Address=46 Register=0x100 regValue_u8=0

[MCU2_0] 10.609171 s: Configuring OVX3C imager 0x46.. Please wait till it finishes

[MCU2_0] 11.147153 s: waiting issUb9702_953_sensor init finsh

[MCU2_0] 11.574071 s: IssUb9702_953_init end status=0

[MCU2_0] 11.574224 s: Receive I2C init success

[MCU2_0] 11.574280 s: MAX20087: POC_EN (150 ticks)

[MCU2_0] 11.575223 s: POC_EN UP!

[MCU2_0] 11.575289 s: MAX20087: POC_EN_WAIT (150 ticks)

[MCU2_0] 11.577268 s: POC_EN wait 100ms up , DO IPC notify!

[MCU2_0] 11.577341 s: MAX20087: USS_EN (0 ticks)

[MCU2_0] 11.578191 s: MAX20087: ALL_OK (0 ticks)

[MCU2_0] 11.579183 s: MAX20087: ALL_OK (0 ticks)

[MCU2_0] 11.591183 s: read_ub953_init_status =0xf

[MCU2_0] 11.591243 s: read_sensor_init_status =0xf

[MCU2_0] 11.624549 s: [read_camera_para] ch0 rd_flag =1

[MCU2_0] 11.657854 s: [read_camera_para] ch1 rd_flag =1

[MCU2_0] 11.691098 s: [read_camera_para] ch2 rd_flag =1

[MCU2_0] 11.724740 s: [read_camera_para] ch3 rd_flag =1

[MCU2_0] 11.724823 s: ===diag_flag_last=0xffff diag_flag=0xf0ff diag_flag_changed=1

[MCU2_0] 11.724879 s: ===CameraTaskDiagCheck TI_GPIO_9702_TDA_CAM_A_ERR_MASK_BIT

[MCU2_0] 11.774798 s: [sensor_dtc_handler] sensor stream off

[MCU2_0] 11.774879 s: ===CameraTaskDiagCheck TI_GPIO_9702_TDA_CAM_B_ERR_MASK_BIT

[MCU2_0] 11.824796 s: [sensor_dtc_handler] sensor stream off

[MCU2_0] 11.824882 s: ===CameraTaskDiagCheck TI_GPIO_9702_TDA_CAM_C_ERR_MASK_BIT

[MCU2_0] 11.874796 s: [sensor_dtc_handler] sensor stream off

[MCU2_0] 11.874877 s: ===CameraTaskDiagCheck TI_GPIO_9702_TDA_CAM_D_ERR_MASK_BIT

[MCU2_0] 11.924809 s: [sensor_dtc_handler] sensor stream off

[MCU2_0] 11.924886 s: camera task one loop end1

[MCU2_0] 12.176387 s: src/csirx_drv.c @ Line 407:

[MCU2_0] 12.176431 s: Enable monitor ctl

[MCU2_0] 12.341152 s: reSetupI2CInst

[MCU2_0] 12.826224 s: ===diag_flag_last=0xf0ff diag_flag=0xf1ff diag_flag_changed=1

[MCU2_0] 12.826292 s: camera task one loop end1

[MCU2_0] 12.926219 s: ===diag_flag_last=0xf1ff diag_flag=0xf3ff diag_flag_changed=1

[MCU2_0] 12.926288 s: camera task one loop end1

[MCU2_0] 13.026232 s: ===diag_flag_last=0xf3ff diag_flag=0xf7ff diag_flag_changed=1

[MCU2_0] 13.026304 s: camera task one loop end1

[MCU2_0] 13.126290 s: ===diag_flag_last=0xf7ff diag_flag=0xffff diag_flag_changed=1

[MCU2_0] 13.126403 s: camera task one loop end1

[MCU2_0] 16.474997 s: [UDMA]

[MCU2_0] 16.475064 s: [Error] UDMA TX teardown failed!!

[MCU2_0] 16.475154 s: [UDMA]

[MCU2_0] 16.475182 s: [Error] UDMA TX force disable failed!!

[MCU2_0] 16.475228 s: src/csitx_drv.c @ Line 1464:

[MCU2_0] 16.475263 s: [ERROR]UDMA TX channel disable FAILED!!!

[MCU2_0] 16.475311 s: VX_ZONE_ERROR:[tivxCsitxDelete:988] CSITX: ERROR: FVID2 Csitx not stopped !!!

[MCU2_0] 16.632875 s: src/csitx_drv.c @ Line 193:

[MCU2_0] 16.632943 s: Provided instance is already in use

[MCU2_0] 16.632999 s: src/csitx_drv.c @ Line 331:

[MCU2_0] 16.633049 s: Create failed for given configuration

[MCU2_0] 16.633094 s: src/fvid2_drvMgr.c @ Line 759:

[MCU2_0] 16.633182 s: Driver create failed!!

[MCU2_0] 16.633227 s: VX_ZONE_ERROR:[tivxCsitxCreate:825] : Csitx Create Failed!!!

[MCU2_0] 51.026226 s: ===diag_flag_last=0xffff diag_flag=0xfffb diag_flag_changed=1

[MCU2_0] 51.026302 s: ===CameraTaskDiagCheck TI_GPIO_9702_TDA_INTB_MASK_BIT

[MCU2_0] 51.068081 s: video not sync error debonce_count = 1

[MCU2_0] 51.068305 s: camera task one loop end1

[MCU2_0] 51.118660 s: ===diag_flag_last=0xfffb diag_flag=0xffff diag_flag_changed=1

[MCU2_0] 51.118952 s: camera task one loop end1

[MCU2_0] 170.434273 s: DHCP client timed out. Retrying.....

[MCU2_0] 338.434273 s: DHCP client timed out. Retrying.....

[MCU2_1] 5.104146 s: delay done!

[MCU2_1] 5.104247 s: delay done!

[MCU2_1] 5.106320 s: delay done!

[MCU2_1] 6.514914 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[s] mcu3_0[P]

[MCU2_1] 13.386180 s: TIMEOUT: topazdd_wait_on_sync timed out waiting for writeback 0x05a50000.

[MCU2_1] 13.386233 s: topaz mtx context setup command failed

[MCU3_0] 6.479800 s: CIO: Init ... Done !!!

[MCU3_0] 6.479866 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz>

[MCU3_0] 6.479909 s: APP: Init ... !!!

[MCU3_0] 6.479929 s:

[MCU3_0] 6.479941 s: MCU3_0 VERSION INFO

[MCU3_0] 6.479959 s: =======================

[MCU3_0] 6.479977 s:

[MCU3_0] 6.479987 s: #BUILD DATE: 2023-02-28

[MCU3_0] 6.480006 s: #BUILD TIME: 11:11:48

[MCU3_0] 6.480023 s: #BUILD USER: jenkins@murg

[MCU3_0] 6.480041 s: #BUILD BRANCH: murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[MCU3_0] 6.480069 s: #BUILD PROFILE: release

[MCU3_0] 6.480087 s: #BUILD VERSION: R04d00

[MCU3_0] 6.480104 s:

[MCU3_0] 6.480114 s: =======================

[MCU3_0] 6.480130 s:

[MCU3_0] 6.480140 s: =======================

[MCU3_0] 6.480157 s: writing system info... base addr daff020c

[MCU3_0] 6.480181 s: date addr daff020c is 2023-02-28

[MCU3_0] 6.480203 s: time addr daff0218 is 11:11:48

[MCU3_0] 6.480223 s: project addr daff0224 is murgab_PAS/milestone/ZK_BXPECU_PAPUPP1_R04d00

[MCU3_0] 6.480255 s: version addr daff0244 is R04d00

[MCU3_0] 6.480276 s: done!

[MCU3_0] 6.480287 s: =======================

[MCU3_0] 6.480304 s: SCICLIENT: Init ... !!!

[MCU3_0] 6.480567 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[MCU3_0] 6.480602 s: SCICLIENT: DMSC FW revision 0x15

[MCU3_0] 6.480625 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU3_0] 6.480649 s: SCICLIENT: Init ... Done !!!

[MCU3_0] 6.480669 s: MEM: Init ... !!!

[MCU3_0] 6.480696 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e6000000 of size 8388608 bytes !!!

[MCU3_0] 6.480742 s: MEM: Init ... Done !!!

[MCU3_0] 6.480760 s: IPC: Init ... !!!

[MCU3_0] 6.480785 s: IPC: 8 CPUs participating in IPC !!!

[MCU3_0] 6.488125 s: IPC: Init ... Done !!!

[MCU3_0] 6.488181 s: APP: Temp skip syncing with 7 CPUs ... !!!

[MCU3_0] 6.488211 s: REMOTE_SERVICE: Init ... !!!

[MCU3_0] 6.489218 s: REMOTE_SERVICE: Init ... Done !!!

[MCU3_0] 6.489270 s: APP_INIT: uCom_To_Ipc init Func Call... !!!

[MCU3_0] 6.489300 s: [uCom_To_Ipc_Init] ucom_to_ipc_self_cpu_id = 5 ... !!!

[MCU3_0] 6.489330 s: uCom_to_ipc: Init ... Start !!!

[MCU3_0] 6.489354 s: [uCom_To_Ipc_Init] num_cpus = 5 ... !!!

[MCU3_0] 6.489378 s: [uCom_To_Ipc_Init] self_cpu_id = 5 ... !!!

[MCU3_0] 6.489402 s: uCom to IPC: Init ... !!!

[MCU3_0] 6.489425 s: uCom to IPC: 5 CPUs participating in IPC !!!

[MCU3_0] 6.489968 s: uCom to IPC: Init ... Done !!!

[MCU3_0] 6.490013 s: uCom_to_ipc: Init ... Done !!!

[MCU3_0] 6.490056 s: [xxx] mcu2_0 i2c init start

[MCU3_0] 6.490080 s: APP: Init ... Done !!!

[MCU3_0] 6.490099 s: APP: Run ... !!!

[MCU3_0] 6.490117 s: IPC: Starting echo test ...

[MCU3_0] 6.492423 s: APP: Run ... Done !!!

[MCU3_0] 6.492678 s: uCom to IPC: register notify handler.

[MCU3_0] 6.513009 s: [FusionMain] delay 4s

[MCU3_0] 6.514942 s: IPC: Echo status: mpu1_0[x] mcu2_0[.] mcu2_1[.] mcu3_0[s]

[MCU3_0] 6.515032 s: IPC: Echo status: mpu1_0[x] mcu2_0[.] mcu2_1[.] mcu3_0[s]

[MCU3_0] 6.515095 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[.] mcu3_0[s]

[MCU3_0] 6.515154 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[.] mcu3_0[s]

[MCU3_0] 6.515208 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[s]

[MCU3_0] 10.512878 s: delay done!

[C6x_1 ] 6.514555 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_2 ] 6.514568 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] C66X_1[P] C66X_2[s] C7X_1[P]

[MCU2_0] 506.435258 s: DHCP client timed out. Retrying.....

[MCU2_0] 674.437282 s: DHCP client timed out. Retrying.....

[MCU2_0] 842.438435 s: DHCP client timed out. Retrying.....

[MCU2_0] 1010.440389 s: DHCP client timed out. Retrying.....

[MCU2_0] 1178.443428 s: DHCP client timed out. Retrying.....

[MCU2_0] 1346.443308 s: DHCP client timed out. Retrying.....

The laws found in the testing process are as follows:

1. One third of PECUs have this problem at normal temperature

2. Some PECUs will not have problems at normal temperature, and this log will occur after power-on at a low temperature of -40 degrees

3. This problem rarely occurs in some PECUs under any temperature environment

Based on the above test, we currently have the following questions:

1. What causes this UDMA to fail? Have you ever had a client in this situation before?

2. What submodules will be affected if UDMA TX fails to be displayed in log? Will it break video input?

3. Why does temperature affect the probability of error?

4. Is there a quick way to locate the problem?

Best wishes