Other Parts Discussed in Thread: TMDS64EVM, SYSCONFIG

Hi,

I'm working on AM64 EVM with SDK 08_02_00_31.

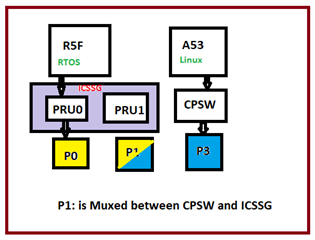

For UDP transmission and reception I'm working with the LWIP module according to your examples.

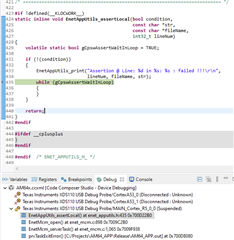

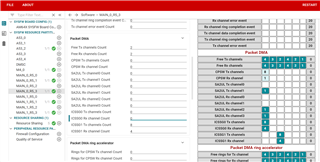

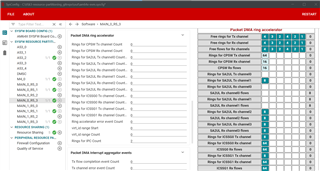

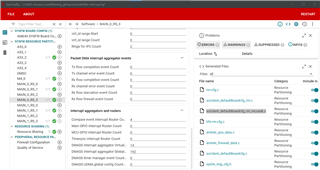

When I run it on R5 stand alone it runs properly but if I activate it when A53 is also running I get a failure from EnetMcm_open due to DMA open failure, printscreens attached.

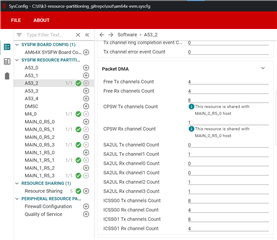

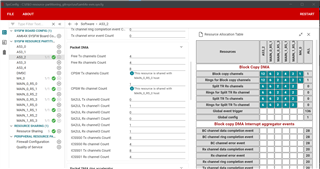

I guess it related to the DTB file in the A53 which probably should disable any resource to let the R5 the ability to use it.

Please review it and advise.

Thanks,

Dekel