TI Team,

I am reviewing the LCDC user guide and wanted to make sure I can drive a display without using hysnc and vsync and only a data enable signal. The LCDC datasheet seems to imply this in section 2.1.4 but it doesn't go into detail of how this happens. I am making the assumption that the LCDC controller always sends out hsync, vsync, and data enable (DE) in active tft mode?

If we want to run in DE mode, what are the appropriate register values that need to be programmed?

- There does not seem to be any setting that indicates run in DE mode.

- In DE mode there is no H front porch, H back porch, H pulse width, V front porch, B back porch, and V pulse width. How are RASTER_TIMING_0 and RASTER_TIMING_1 registers supposed to be programmed to accomplish DE mode functionality? I am assuming that the DE timing is based off of the H front porch, H back porch and H pulse width?

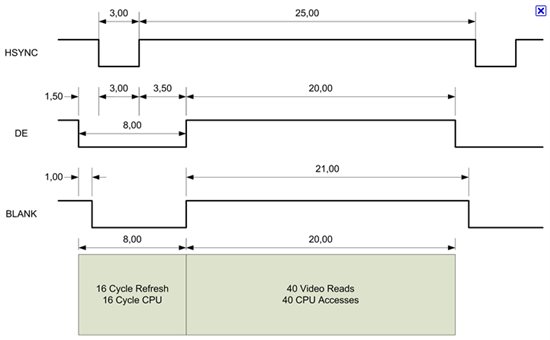

I did not see a timing diagram like this and wanted to make sure we can use this controller in this fashion as shown in the picture (Disregard the timings in the picture):