Hi TI Team,

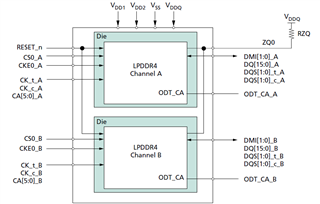

The LPDDR4 used on our ECU is MT53E1G32D2FW , and its array configuration is 2 channels ×16 I/O × 1 rank.

There is a question about the DDR Data Rate:

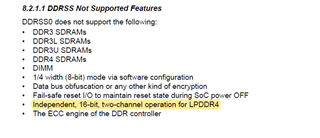

I noticed that DDRSS not support Independent, 16-bit, two-channel operation for LPDDR4 as below.

Does it mean that TDA4 can only read and write with one DDR channel at the same time?

But we connect CA_A and CA_B of DDR together, in this case, can we enable two channels to read and write at the same time?

For DDR the max data rate is 4266Mb/s per pin , In the case of dual-channel DDR4, is the maximum data rate of TDA4 and DDR 4266*16 or 4266*32?

Regards,

Shuwei