Hi,

is it possible to output 100MHz clock from SERDES0_REFCLK_P & SERDES0_REFCLK_N pins on TDA4VE (j721s2)?

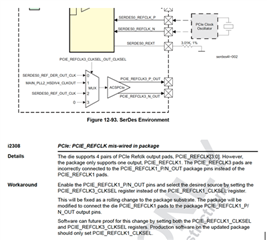

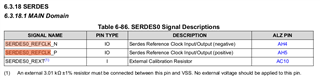

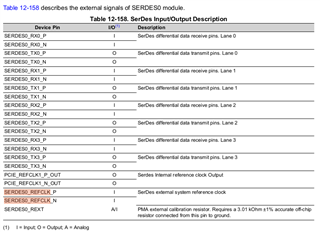

TDA4VE-Q1 datasheet (SPRSP62) lists SERDES0_REFCLK_P & SERDES0_REFCLK_N as IO (input/output) pin type:

However, J721S2 TDA4VE TRM (SPRUJ08C) list those two pins as input only (not capable of clock output):

Could you clarify which one is correct?

And if clock output is possible, where to find details on how to do so?

BR,

Primoz

CC: Robert Eschler