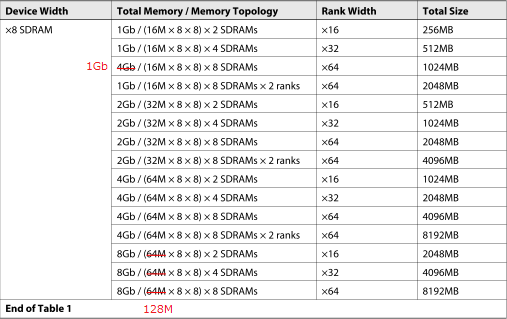

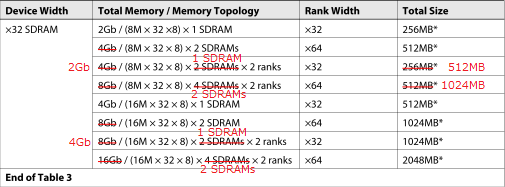

DDR3 Design Requirement for Keystone Devices p11 Table

I do not understand some part of the table.

Device Width Total Memory / Memory Topology Rank Width Total Size

x8 SDRAM 1Gb / (16M x 8 x 8) x 4 SDRAMS x32 512MB (2nd row of Table 1)

Column1 (Device width): This is the data width of the DDR3 SDRAM. Currently available are x8, x16, x32.

Column2 (Total Memory/Memory Topology): I do not understand this column.

I understand that 16M (number of memory locations per bank) x 8 (device width) x 8 (number of banks) is the configuration for the DDR3 SDRAM.

But I do not understand the 1Gb. Initially I understand it to be 1Gb=16M*8*8 but 3rd row (4Gb / (16M x 8 x 8)) and other rows below proves otherwise. Could it be a typo?

I understand x2 SDRAMs to be the number of SDRAM for that topology. x8 SDRAMs x 2 Ranks => x 16 SDRAMs.

Column3 (Rank width): I do not understand this column.

Rank width seems to be the device width * number of SDRAM. However, some rows (row 3, 4, 7, 8 in Table 3) again prove otherwise.

Column 4(Total size): I do not understand this column.

Total size seems to be memory size * number of RAM used. However, some row (row 3, 4, 7, 8 in Table 3) again prove otherwise.

I suspect there is a lot of typo in p11 and p12. Pls help to clarify to confirm my understanding. Thanks.