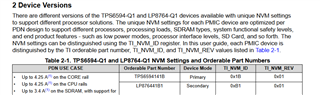

I am trying to disable the watchdog during runtime ( there are some use cases where we need to disable to watchdog before jumping to bootloader for flashing, during debugging etc..)

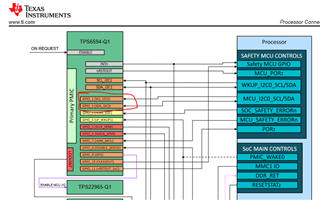

Looking at the manual, there is a need to use DISABLE_WDOG Pin. This pin is used in our design as an output, I believe this is not available for us to use.

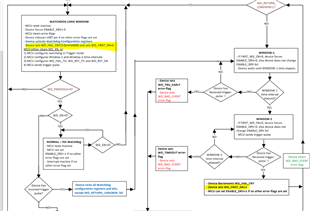

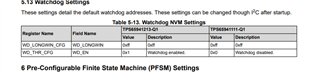

Is there any other recommended sequence that can be followed to disable or turn off the watchdog. Like going to long window and then disabling the WD_EN pin??