Other Parts Discussed in Thread: TMDS64EVM

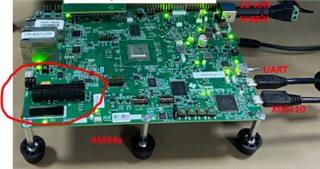

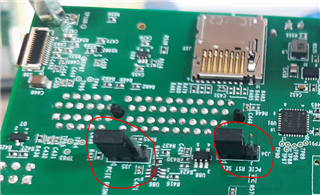

We're evaluating the am6441 to implement a PCIe "add-in" board contain a bunch of custom serial communication logic.

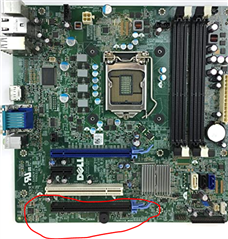

I've run the PCIe benchmark between two EVM boards, and now I'm trying to do similar testing with TMDS64EVM as an endpoint connected to a PC motherboard.

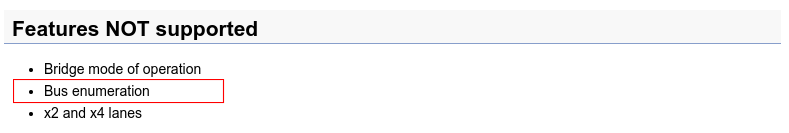

However, it has become apparent that neither the endpoint nor root-complex example apps in the am64 SDK support PCIe bus enumeration. The example apps are all based on a degenerate PCIe case where endpoints don't have config registers and all PCIe memory map assignments are known at compile time by both the RC and EP(s). Because of this the PC's OS doesn't recognize the MDS64EVM endpoint at all, and the example apps aren't useful for any sort of real-world use-case testing.

Is there any documentation, examples, tips, or clues on how to support normal PCIe bus enumeration in an am64x endpoint?