Hi team,

SDK version: 8.5

Platform: Tda4 eco

Phy: 88EA1512

Because the platform has two identical PHYs attached (different phy addr), the one in the MCU domain is ready to acquire IP, connect the network cable and power on (CLK:25M->125M).

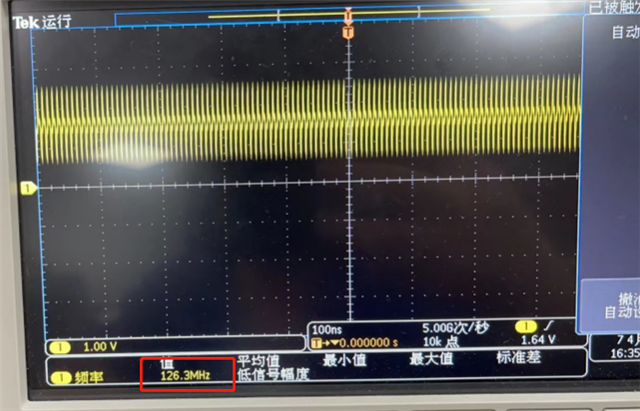

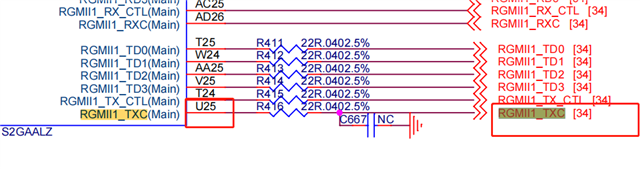

Please see the MCU below:

When debugging phy in the Linux main domain and getting IP with udhcpc, the IP is not available and the static IP is not pinged.

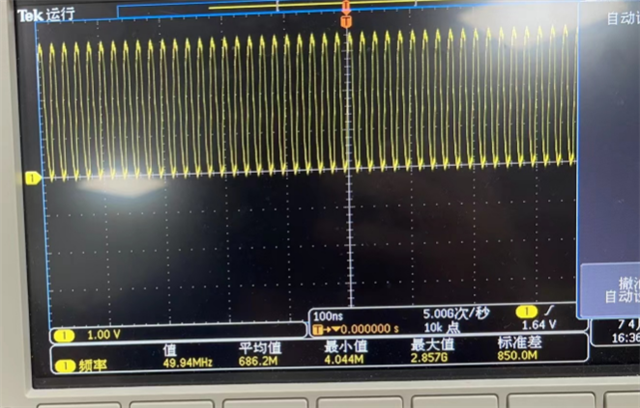

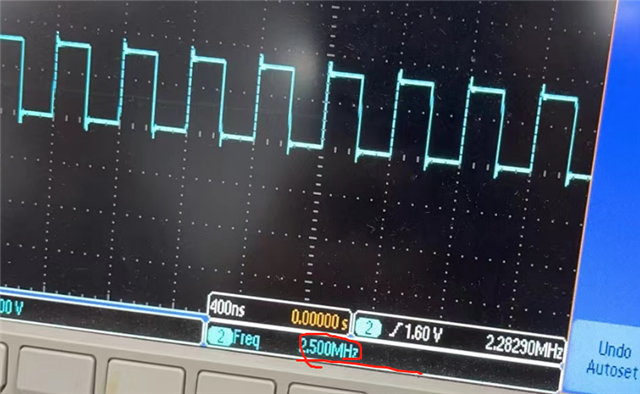

When debugging the chip, the RGMII output was found to be: Powered on with the network cable (CLK:10M-> 50M).

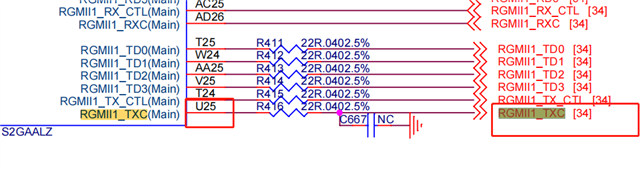

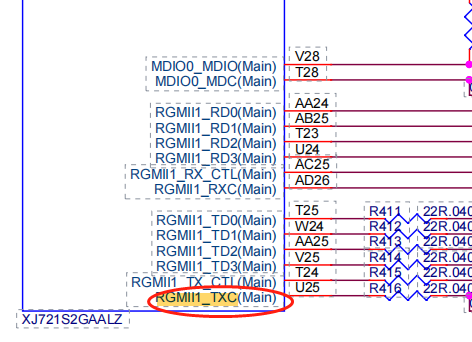

The following figure shows the pin diagram main domain:

root@j721s2-evm:~# ifconfig

docker0: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500 metric 1

inet 172.17.0.1 netmask 255.255.0.0 broadcast 172.17.255.255

ether 02:42:18:fd:36:15 txqueuelen 0 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth0: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500 metric 1

ether 34:08:e1:84:a1:a1 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth1: flags=4163<UP,BROADCAST,RUNNING,MULTICAST> mtu 1500 metric 1

inet6 fe80::1cdf:d9ff:fe76:de18 prefixlen 64 scopeid 0x20<link>

ether 1e:df:d9:76:de:18 txqueuelen 1000 (Ethernet)

RX packets 41974 bytes 2772905 (2.6 MiB)

RX errors 0 dropped 60 overruns 0 frame 0

TX packets 63 bytes 12834 (12.5 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536 metric 1

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10<host>

loop txqueuelen 1000 (Local Loopback)

RX packets 82 bytes 6220 (6.0 KiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 82 bytes 6220 (6.0 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

root@j721s2-evm:~# udhcpc -i eth1

udhcpc: started, v1.31.1

udhcpc: sending discover

udhcpc: sending discover

udhcpc: sending discover

udhcpc: sending discover

udhcpc: sending discover

udhcpc: sending discover

Dts used is as follows:

main_cpsw: ethernet@c200000 {

compatible = "ti,j721e-cpsw-nuss";

#address-cells = <2>;

#size-cells = <2>;

reg = <0x0 0xc200000 0x0 0x200000>;

reg-names = "cpsw_nuss";

ranges = <0x0 0x0 0x0 0xc200000 0x0 0x200000>;

dma-coherent;

clocks = <&k3_clks 28 28>;

clock-names = "fck";

power-domains = <&k3_pds 28 TI_SCI_PD_EXCLUSIVE>;

dmas = <&main_udmap 0xc640>,

<&main_udmap 0xc641>,

<&main_udmap 0xc642>,

<&main_udmap 0xc643>,

<&main_udmap 0xc644>,

<&main_udmap 0xc645>,

<&main_udmap 0xc646>,

<&main_udmap 0xc647>,

<&main_udmap 0x4640>;

dma-names = "tx0", "tx1", "tx2", "tx3",

"tx4", "tx5", "tx6", "tx7",

"rx";

ethernet-ports {

#address-cells = <1>;

#size-cells = <0>;

main_cpsw_port1: port@1 {

reg = <1>;

ti,mac-only;

label = "port1";

phys = <&phy_gmii_sel_cpsw 1>;

};

};

main_cpsw_mdio: mdio@f00 {

compatible = "ti,cpsw-mdio","ti,davinci_mdio";

reg = <0x0 0xf00 0x0 0x100>;

#address-cells = <1>;

#size-cells = <0>;

clocks = <&k3_clks 28 28>;

clock-names = "fck";

bus_freq = <1000000>;

};

cpts@3d000 {

compatible = "ti,am65-cpts";

reg = <0x0 0x3d000 0x0 0x400>;

clocks = <&k3_clks 28 3>;

clock-names = "cpts";

interrupts-extended = <&gic500 GIC_SPI 21 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "cpts";

ti,cpts-ext-ts-inputs = <4>;

ti,cpts-periodic-outputs = <2>;

};

};

scm_conf: scm-conf@104000 {

phy_gmii_sel_cpsw: phy@34 {

compatible = "ti,am654-phy-gmii-sel";

reg = <0x34 0x4>;

#phy-cells = <1>;

};

};

main_cpsw {

// status="disabled";

pinctrl-names = "default";

pinctrl-0 = <&main_cpsw_pins_default>,<&main_mdio_pins_default>/*,<&phy_reset_pins_default>*/;

};

&main_cpsw_mdio {

phy1: ethernet-phy@1 {

reg = <1>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,min-output-impedance;

// compatible = "marvell,88E1510", "ethernet-phy-id0141.0DD1", "ethernet-phy-ieee802.3-c22";

// device_type = "ethernet-phy";

// marvell,reg-init = <0x12 0x14 0xFFF7 0x2>;

// max-speed = <1000>;

// reset-gpios = <&main_gpio0 21 GPIO_ACTIVE_LOW>;

// ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

// ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

// ti,min-output-impedance;

};

};

&main_cpsw_port1 {

phy-mode = "rgmii-rxid";

phy-handle = <&phy1>;

};

The customer currently believes that the problem should be with the output clock: “Powered on with the network cable (CLK:10M-> 50M)”

How to adjust the clk so that the RGMII output the correct clock like in the MCU domain to get the IP?

Could you help check this case? Thanks.

Best Regards,

Cherry