Other Parts Discussed in Thread: DS90UB960-Q1,

Hello TI Team

I am using 8.04 version TI RTOS SDK to verify the Deserializer DS90UB960-Q1 interface.

I configured TDA4VM soc's with below changes in the device tree and vision_aaps side. Further flash the image with dtbo file in the sd-card to test the deserializer DS90UB960-Q1 interface using I2C utility at linux side .

1) I2C channel 6 configuration enabled at Linux A72 side

2) The required pin muxing changes as per the schematics in the app_pinmux.c file inside the misc utility of the vision_apps application.

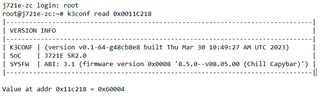

Further I get to know that, using "dmesg | grep i2c" command , my i2c channel 6 is getting configured on the A72 side properly which shows below result.

root@j721e:~# dmesg | grep i2c

[ 0.780435] i2c /dev entries driver

[ 0.995932] omap_i2c 40b00000.i2c: bus 0 rev0.12 at 400 kHz

[ L��02252] omap_i2c 40b10000.i2c: bus 1 rev0.12 at 100 kHz

[ 1.186408] omap_i2c 42120000.i2c: bus 2 rev0.12 at 400 kHz

[ 1.192642] omap_i2c 2020000.i2c: bus 3 rev0.12 at 100 kHz

[ 1.198643] omap_i2c 2040000.i2c: bus 6��gv0.12 at 100 kHz

[ 1.204689] omap_i2c 2050000.i2c: bus 5 rev0.12 at 400 kHz

[ 1.210690] omap_i2c 2060000.i2c: bus 6 rev0.12 at 400 kHz

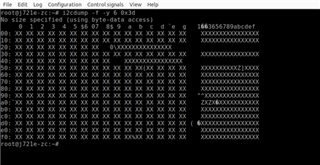

But further I'm not able to get the Deserialiser DS90UB960 data using "i2cdump -f -y 6 0x3d" command.

Also checked the NP Register settings as per the schematics that required to be non populated to configure the Deserialiser DS90UB960 slave ID as 0x3d on actual hardware board.

So could you guys help to solve this issue and to get the Deserializer DS90UB960 data info using I2C utility. Or Any further changes required at device tree side.

- Best regards.