Hello TI colleagues,

Our SDK version is 8.4

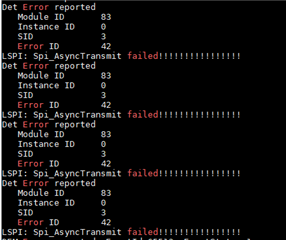

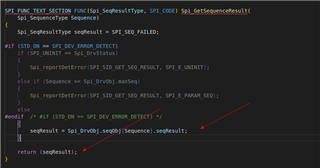

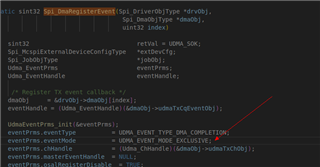

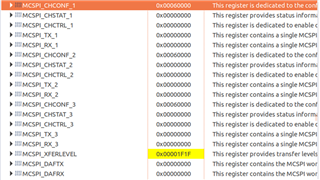

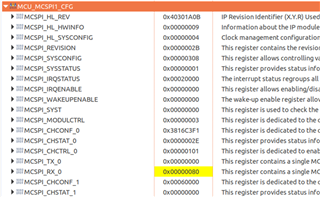

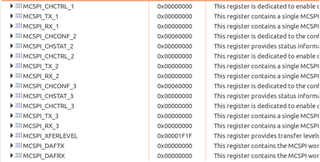

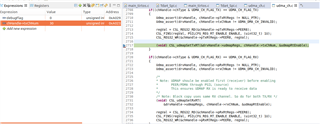

now we met issue when using DMA.

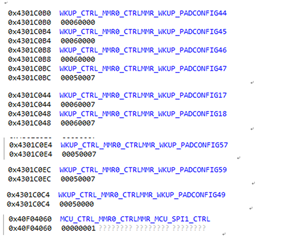

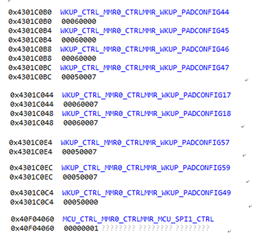

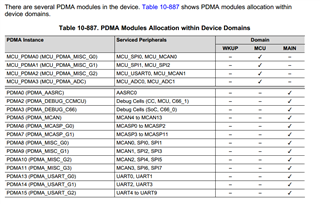

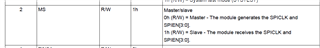

We use SPI DMA transfers in the MCU domain, DMA is also used at TIDL.

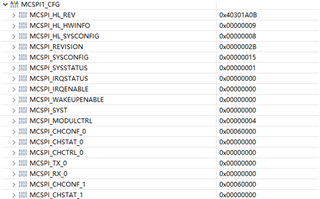

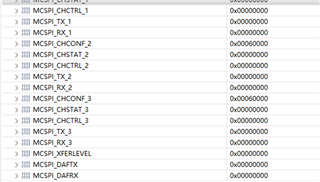

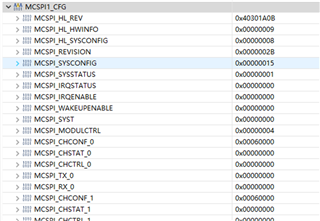

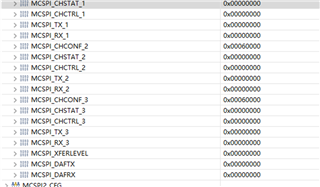

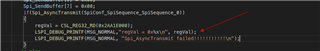

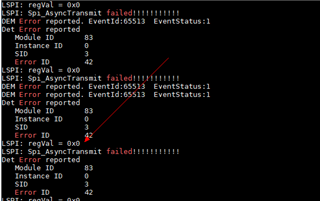

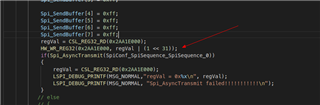

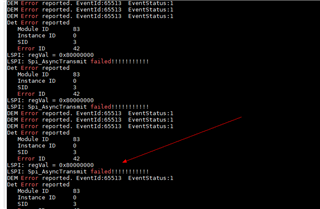

When the app of TIDL is not running, the SPI DMA transfer in the MCU domain is normal, After running the TIDL related app, SPI in the MCU domain could not be read or written. We checked with an oscilloscope and found that SPI_CLK had no output.

When the SPI in the MCU domain does not use DMA transfer, the TIDL related app is run, and the SPI functions normally.

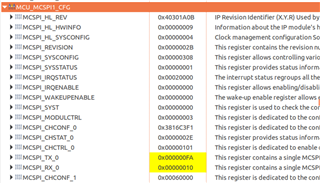

I found that only dmaTxChIntrNum and dmaRxChIntrNum can be configured in MCAL CONFIG of MCU domain. How can we use SPI DMA transfer in MCU domain and run TIDL normally?

Regards,

bingxian