Other Parts Discussed in Thread: TDA4VH

Hi, TI experts,

The hardware we designed needs to control three deserializers on CSI0 1 2 through I2C1, I2C5 and I2C6 respectively. Now we have encountered some problems when running the single cam app:

- For CSI0, the program will be stuck at IssSensor_PowerOn->IssSensor_I2CBusInit->setupI2CInst->I2C_open, and will not continue to execute;

- For CSI1, the registers of the deserializer cannot be written, and I2C5 has no data. For the R core log, please see the attached i2c5-rtos.log;

- The phenomena of CSI2 and CSI1 are the same;

We are using TDA4VH, and the SDK is 0805.

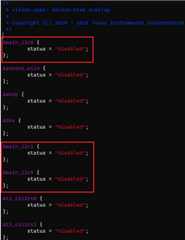

The corresponding i2c node has been disabled in the device tree on the Linux:

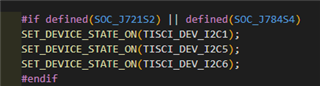

The J784S4_pinmux_data.c and app_pinmux_J784S4.c on the RTOS side have also been modified accordingly. For details, see the attachment j784s4_pinmux_data.diff and app_pinmux_j784s4.diff

The I2cInstId of IssSensor_I2CBusInit() in iss_sensors.c and the i2cInstId of IssSensor_CreateParams in the sensor driver are also modified each time before opening a different CSI.

[MCU2_0] 2.411336 s: CIO: Init ... Done !!! [MCU2_0] 2.411388 s: ### CPU Frequency = 1000000000 Hz [MCU2_0] 2.411418 s: CPU is running FreeRTOS [MCU2_0] 2.411438 s: APP: Init ... !!! [MCU2_0] 2.411458 s: SCICLIENT: Init ... !!! [MCU2_0] 2.411599 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [MCU2_0] 2.411631 s: SCICLIENT: DMSC FW revision 0x8 [MCU2_0] 2.411661 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU2_0] 2.411691 s: SCICLIENT: Init ... Done !!! [MCU2_0] 2.411714 s: UDMA: Init ... !!! [MCU2_0] 2.412669 s: UDMA: Init ... Done !!! [MCU2_0] 2.412703 s: UDMA: Init ... !!! [MCU2_0] 2.413235 s: UDMA: Init for CSITX/CSIRX ... Done !!! [MCU2_0] 2.413275 s: MEM: Init ... !!! [MCU2_0] 2.413310 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ e2000000 of size 16777216 bytes !!! [MCU2_0] 2.413371 s: MEM: Init ... Done !!! [MCU2_0] 2.413394 s: IPC: Init ... !!! [MCU2_0] 2.413444 s: IPC: 11 CPUs participating in IPC !!! [MCU2_0] 2.413485 s: IPC: Waiting for HLOS to be ready ... !!! [MCU2_0] 16.673119 s: IPC: HLOS is ready !!! [MCU2_0] 16.696360 s: IPC: Init ... Done !!! [MCU2_0] 16.696410 s: APP: Syncing with 10 CPUs ... !!! [MCU2_0] 17.075312 s: APP: Syncing with 10 CPUs ... Done !!! [MCU2_0] 17.075351 s: REMOTE_SERVICE: Init ... !!! [MCU2_0] 17.077124 s: REMOTE_SERVICE: Init ... Done !!! [MCU2_0] 17.077163 s: FVID2: Init ... !!! [MCU2_0] 17.077215 s: FVID2: Init ... Done !!! [MCU2_0] 17.077240 s: SCICLIENT: Sciclient_pmSetModuleState module=275 state=2 [MCU2_0] 17.077367 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.077410 s: VHWA: VPAC Init ... !!! [MCU2_0] 17.077490 s: SCICLIENT: Sciclient_pmSetModuleState module=399 state=2 [MCU2_0] 17.077643 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.077672 s: VHWA: LDC Init ... !!! [MCU2_0] 17.083359 s: VHWA: LDC Init ... Done !!! [MCU2_0] 17.083402 s: VHWA: MSC Init ... !!! [MCU2_0] 17.095982 s: VHWA: MSC Init ... Done !!! [MCU2_0] 17.096020 s: VHWA: NF Init ... !!! [MCU2_0] 17.097567 s: VHWA: NF Init ... Done !!! [MCU2_0] 17.097602 s: VHWA: VISS Init ... !!! [MCU2_0] 17.107321 s: VHWA: VISS Init ... Done !!! [MCU2_0] 17.107367 s: VHWA: VPAC Init ... Done !!! [MCU2_0] 17.107406 s: VX_ZONE_INIT:Enabled [MCU2_0] 17.107433 s: VX_ZONE_ERROR:Enabled [MCU2_0] 17.107457 s: VX_ZONE_WARNING:Enabled [MCU2_0] 17.108403 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU2-0 [MCU2_0] 17.108592 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_NF [MCU2_0] 17.108774 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_LDC1 [MCU2_0] 17.108948 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_MSC1 [MCU2_0] 17.109115 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_MSC2 [MCU2_0] 17.109352 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC_VISS1 [MCU2_0] 17.109555 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE1 [MCU2_0] 17.109754 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE2 [MCU2_0] 17.109948 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DISPLAY1 [MCU2_0] 17.110155 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DISPLAY2 [MCU2_0] 17.110350 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CSITX [MCU2_0] 17.110561 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE3 [MCU2_0] 17.110762 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE4 [MCU2_0] 17.110960 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE5 [MCU2_0] 17.111168 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE6 [MCU2_0] 17.111375 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE7 [MCU2_0] 17.111571 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE8 [MCU2_0] 17.111754 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M1 [MCU2_0] 17.111932 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M2 [MCU2_0] 17.112104 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M3 [MCU2_0] 17.112288 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DSS_M2M4 [MCU2_0] 17.112471 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CSITX2 [MCU2_0] 17.112719 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE9 [MCU2_0] 17.112922 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE10 [MCU2_0] 17.113128 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE11 [MCU2_0] 17.113333 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target CAPTURE12 [MCU2_0] 17.113382 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [MCU2_0] 17.113412 s: APP: OpenVX Target kernel init ... !!! [MCU2_0] 17.139674 s: APP: OpenVX Target kernel init ... Done !!! [MCU2_0] 17.139711 s: CSI2RX: Init ... !!! [MCU2_0] 17.139733 s: SCICLIENT: Sciclient_pmSetModuleState module=189 state=2 [MCU2_0] 17.139832 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.139862 s: SCICLIENT: Sciclient_pmSetModuleState module=72 state=2 [MCU2_0] 17.139981 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.140010 s: SCICLIENT: Sciclient_pmSetModuleState module=73 state=2 [MCU2_0] 17.140102 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.140129 s: SCICLIENT: Sciclient_pmSetModuleState module=74 state=2 [MCU2_0] 17.140217 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.140245 s: SCICLIENT: Sciclient_pmSetModuleState module=212 state=2 [MCU2_0] 17.140315 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.140342 s: SCICLIENT: Sciclient_pmSetModuleState module=213 state=2 [MCU2_0] 17.140410 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.140438 s: SCICLIENT: Sciclient_pmSetModuleState module=214 state=2 [MCU2_0] 17.140510 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.140730 s: CSI2RX: Init ... Done !!! [MCU2_0] 17.140758 s: CSI2TX: Init ... !!! [MCU2_0] 17.140780 s: SCICLIENT: Sciclient_pmSetModuleState module=189 state=2 [MCU2_0] 17.140880 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.140907 s: SCICLIENT: Sciclient_pmSetModuleState module=75 state=2 [MCU2_0] 17.141016 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.141044 s: SCICLIENT: Sciclient_pmSetModuleState module=76 state=2 [MCU2_0] 17.141157 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.141185 s: SCICLIENT: Sciclient_pmSetModuleState module=402 state=2 [MCU2_0] 17.141249 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 17.141322 s: CSI2TX: Init ... Done !!! [MCU2_0] 17.141349 s: ISS: Init ... !!! [MCU2_0] 17.141374 s: Found sensor GW_IMX390_UYVY at location 0 [MCU2_0] 17.141410 s: Found sensor GW_AR0233_MAX96717_UYVY at location 1 [MCU2_0] 17.141445 s: Found sensor GW_AR0233_MAX96717_MULTI at location 2 [MCU2_0] 17.141479 s: Found sensor GW_X8B_MAX9295_UYVY at location 3 [MCU2_0] 17.141512 s: Found sensor OS_AR0233_MAX9295_MARS at location 4 [MCU2_0] 17.141545 s: Found sensor OS_AR0820_MAX9295_LI_MULTI at location 5 [MCU2_0] 17.141580 s: Found sensor OS_AR0820A_MAX9295_LI at location 6 [MCU2_0] 17.141613 s: Found sensor OVX3C-MAX9295_MARS at location 7 [MCU2_0] 17.141646 s: Found sensor OVX3C-MAX9295_MARS_MULTI at location 8 [MCU2_0] 17.141680 s: Found sensor OVX3CF-MAX96717_MARS at location 9 [MCU2_0] 17.141714 s: Found sensor OVX3CF-MAX96717_MARS_MULTI at location 10 [MCU2_0] 17.141747 s: IssSensor_Init ... Done !!! [MCU2_0] 17.141808 s: IttRemoteServer_Init ... Done !!! [MCU2_0] 17.141836 s: VISS REMOTE SERVICE: Init ... !!! [MCU2_0] 17.141891 s: VISS REMOTE SERVICE: Init ... Done !!! [MCU2_0] 17.141919 s: UDMA Copy: Init ... !!! [MCU2_0] 17.142945 s: UDMA Copy: Init ... Done !!! [MCU2_0] 17.143017 s: APP: Init ... Done !!! [MCU2_0] 17.143045 s: APP: Run ... !!! [MCU2_0] 17.143067 s: IPC: Starting echo test ... [MCU2_0] 17.148417 s: APP: Run ... Done !!! [MCU2_0] 17.150045 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[.] mcu3_1[.] mcu4_0[.] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_0] 17.150173 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[.] mcu4_0[.] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_0] 17.150285 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[.] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_0] 17.150397 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_0] 17.150508 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_0] 17.150618 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_0] 17.150727 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[.] c7x_4[.] [MCU2_0] 17.150837 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[.] [MCU2_0] 17.150946 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU2_1] 2.382892 s: CIO: Init ... Done !!! [MCU2_1] 2.382943 s: ### CPU Frequency = 1000000000 Hz [MCU2_1] 2.382977 s: CPU is running FreeRTOS [MCU2_1] 2.382999 s: APP: Init ... !!! [MCU2_1] 2.383018 s: SCICLIENT: Init ... !!! [MCU2_1] 2.383171 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [MCU2_1] 2.383206 s: SCICLIENT: DMSC FW revision 0x8 [MCU2_1] 2.383234 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU2_1] 2.383266 s: SCICLIENT: Init ... Done !!! [MCU2_1] 2.383289 s: UDMA: Init ... !!! [MCU2_1] 2.384397 s: UDMA: Init ... Done !!! [MCU2_1] 2.384437 s: MEM: Init ... !!! [MCU2_1] 2.384472 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ e3000000 of size 16777216 bytes !!! [MCU2_1] 2.384535 s: MEM: Init ... Done !!! [MCU2_1] 2.384558 s: IPC: Init ... !!! [MCU2_1] 2.384602 s: IPC: 11 CPUs participating in IPC !!! [MCU2_1] 2.384640 s: IPC: Waiting for HLOS to be ready ... !!! [MCU2_1] 16.712302 s: IPC: HLOS is ready !!! [MCU2_1] 16.734909 s: IPC: Init ... Done !!! [MCU2_1] 16.734959 s: APP: Syncing with 10 CPUs ... !!! [MCU2_1] 17.075310 s: APP: Syncing with 10 CPUs ... Done !!! [MCU2_1] 17.075346 s: REMOTE_SERVICE: Init ... !!! [MCU2_1] 17.077209 s: REMOTE_SERVICE: Init ... Done !!! [MCU2_1] 17.077250 s: FVID2: Init ... !!! [MCU2_1] 17.077312 s: FVID2: Init ... Done !!! [MCU2_1] 17.077339 s: VHWA: DMPAC: Init ... !!! [MCU2_1] 17.077363 s: SCICLIENT: Sciclient_pmSetModuleState module=92 state=2 [MCU2_1] 17.077539 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_1] 17.077570 s: SCICLIENT: Sciclient_pmSetModuleState module=96 state=2 [MCU2_1] 17.077902 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_1] 17.077929 s: VHWA: DOF Init ... !!! [MCU2_1] 17.085121 s: VHWA: DOF Init ... Done !!! [MCU2_1] 17.085165 s: VHWA: SDE Init ... !!! [MCU2_1] 17.087310 s: VHWA: SDE Init ... Done !!! [MCU2_1] 17.087345 s: VHWA: DMPAC: Init ... Done !!! [MCU2_1] 17.087382 s: VX_ZONE_INIT:Enabled [MCU2_1] 17.087407 s: VX_ZONE_ERROR:Enabled [MCU2_1] 17.087431 s: VX_ZONE_WARNING:Enabled [MCU2_1] 17.088383 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU2-1 [MCU2_1] 17.088604 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DMPAC_SDE [MCU2_1] 17.088810 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target DMPAC_DOF [MCU2_1] 17.088858 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [MCU2_1] 17.088889 s: APP: OpenVX Target kernel init ... !!! [MCU2_1] 17.089146 s: APP: OpenVX Target kernel init ... Done !!! [MCU2_1] 17.089182 s: APP: Init ... Done !!! [MCU2_1] 17.089206 s: APP: Run ... !!! [MCU2_1] 17.089227 s: IPC: Starting echo test ... [MCU2_1] 17.093916 s: APP: Run ... Done !!! [MCU2_1] 17.095180 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[.] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_1] 17.095298 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_1] 17.095401 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_1] 17.095504 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[.] c7x_3[.] c7x_4[.] [MCU2_1] 17.095612 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[.] c7x_4[.] [MCU2_1] 17.095717 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[.] [MCU2_1] 17.095820 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU2_1] 17.147606 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU2_1] 17.149062 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[s] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_0] 2.391591 s: CIO: Init ... Done !!! [MCU3_0] 2.391645 s: ### CPU Frequency = 1000000000 Hz [MCU3_0] 2.391677 s: CPU is running FreeRTOS [MCU3_0] 2.391698 s: APP: Init ... !!! [MCU3_0] 2.391718 s: SCICLIENT: Init ... !!! [MCU3_0] 2.391864 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [MCU3_0] 2.391900 s: SCICLIENT: DMSC FW revision 0x8 [MCU3_0] 2.391929 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU3_0] 2.391959 s: SCICLIENT: Init ... Done !!! [MCU3_0] 2.391982 s: MEM: Init ... !!! [MCU3_0] 2.392013 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ e4000000 of size 8388608 bytes !!! [MCU3_0] 2.392071 s: MEM: Init ... Done !!! [MCU3_0] 2.392092 s: IPC: Init ... !!! [MCU3_0] 2.392137 s: IPC: 11 CPUs participating in IPC !!! [MCU3_0] 2.392174 s: IPC: Waiting for HLOS to be ready ... !!! [MCU3_0] 16.655787 s: IPC: HLOS is ready !!! [MCU3_0] 16.679792 s: IPC: Init ... Done !!! [MCU3_0] 16.679838 s: APP: Syncing with 10 CPUs ... !!! [MCU3_0] 17.075311 s: APP: Syncing with 10 CPUs ... Done !!! [MCU3_0] 17.075348 s: REMOTE_SERVICE: Init ... !!! [MCU3_0] 17.076979 s: REMOTE_SERVICE: Init ... Done !!! [MCU3_0] 17.077031 s: VX_ZONE_INIT:Enabled [MCU3_0] 17.077054 s: VX_ZONE_ERROR:Enabled [MCU3_0] 17.077076 s: VX_ZONE_WARNING:Enabled [MCU3_0] 17.078003 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU3-0 [MCU3_0] 17.078051 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [MCU3_0] 17.078081 s: APP: OpenVX Target kernel init ... !!! [MCU3_0] 17.078107 s: APP: OpenVX Target kernel init ... Done !!! [MCU3_0] 17.078132 s: APP: Init ... Done !!! [MCU3_0] 17.078154 s: APP: Run ... !!! [MCU3_0] 17.078174 s: IPC: Starting echo test ... [MCU3_0] 17.082825 s: APP: Run ... Done !!! [MCU3_0] 17.084047 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[s] mcu3_1[.] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[.] c7x_3[.] c7x_4[.] [MCU3_0] 17.084191 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[s] mcu3_1[.] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[.] c7x_4[.] [MCU3_0] 17.084302 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[s] mcu3_1[.] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[.] [MCU3_0] 17.084404 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[s] mcu3_1[.] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_0] 17.084551 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[s] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_0] 17.084658 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[s] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_0] 17.094495 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[s] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_0] 17.147549 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[s] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_0] 17.149078 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[s] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_1] 2.402248 s: CIO: Init ... Done !!! [MCU3_1] 2.402299 s: ### CPU Frequency = 1000000000 Hz [MCU3_1] 2.402332 s: CPU is running FreeRTOS [MCU3_1] 2.402352 s: APP: Init ... !!! [MCU3_1] 2.402371 s: SCICLIENT: Init ... !!! [MCU3_1] 2.402515 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [MCU3_1] 2.402551 s: SCICLIENT: DMSC FW revision 0x8 [MCU3_1] 2.402579 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU3_1] 2.402609 s: SCICLIENT: Init ... Done !!! [MCU3_1] 2.402633 s: MEM: Init ... !!! [MCU3_1] 2.402664 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ e4800000 of size 8388608 bytes !!! [MCU3_1] 2.402722 s: MEM: Init ... Done !!! [MCU3_1] 2.402744 s: IPC: Init ... !!! [MCU3_1] 2.402790 s: IPC: 11 CPUs participating in IPC !!! [MCU3_1] 2.402829 s: IPC: Waiting for HLOS to be ready ... !!! [MCU3_1] 16.793330 s: IPC: HLOS is ready !!! [MCU3_1] 16.815916 s: IPC: Init ... Done !!! [MCU3_1] 16.815961 s: APP: Syncing with 10 CPUs ... !!! [MCU3_1] 17.075312 s: APP: Syncing with 10 CPUs ... Done !!! [MCU3_1] 17.075349 s: REMOTE_SERVICE: Init ... !!! [MCU3_1] 17.077079 s: REMOTE_SERVICE: Init ... Done !!! [MCU3_1] 17.077132 s: VX_ZONE_INIT:Enabled [MCU3_1] 17.077156 s: VX_ZONE_ERROR:Enabled [MCU3_1] 17.077178 s: VX_ZONE_WARNING:Enabled [MCU3_1] 17.078107 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU3-1 [MCU3_1] 17.078156 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [MCU3_1] 17.078186 s: APP: OpenVX Target kernel init ... !!! [MCU3_1] 17.078213 s: APP: OpenVX Target kernel init ... Done !!! [MCU3_1] 17.078239 s: APP: Init ... Done !!! [MCU3_1] 17.078261 s: APP: Run ... !!! [MCU3_1] 17.078281 s: IPC: Starting echo test ... [MCU3_1] 17.083011 s: APP: Run ... Done !!! [MCU3_1] 17.084231 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[s] mcu4_0[x] mcu4_1[.] c7x_1[.] c7x_2[P] c7x_3[.] c7x_4[.] [MCU3_1] 17.084349 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[s] mcu4_0[x] mcu4_1[.] c7x_1[.] c7x_2[P] c7x_3[P] c7x_4[.] [MCU3_1] 17.084454 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[s] mcu4_0[x] mcu4_1[.] c7x_1[.] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_1] 17.084569 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[s] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_1] 17.084671 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[s] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_1] 17.084774 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[s] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_1] 17.094515 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[s] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_1] 17.147570 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[s] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU3_1] 17.149093 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] mcu3_1[s] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_0] 2.453925 s: CIO: Init ... Done !!! [MCU4_0] 2.453981 s: ### CPU Frequency = 1000000000 Hz [MCU4_0] 2.454013 s: CPU is running FreeRTOS [MCU4_0] 2.454036 s: APP: Init ... !!! [MCU4_0] 2.454056 s: SCICLIENT: Init ... !!! [MCU4_0] 2.454202 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [MCU4_0] 2.454236 s: SCICLIENT: DMSC FW revision 0x8 [MCU4_0] 2.454266 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU4_0] 2.454299 s: SCICLIENT: Init ... Done !!! [MCU4_0] 2.454324 s: UDMA: Init ... !!! [MCU4_0] 2.455383 s: UDMA: Init ... Done !!! [MCU4_0] 2.455419 s: MEM: Init ... !!! [MCU4_0] 2.455452 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ e5000000 of size 8388608 bytes !!! [MCU4_0] 2.455511 s: MEM: Init ... Done !!! [MCU4_0] 2.455540 s: IPC: Init ... !!! [MCU4_0] 2.455586 s: IPC: 11 CPUs participating in IPC !!! [MCU4_0] 2.455626 s: IPC: Waiting for HLOS to be ready ... !!! [MCU4_0] 16.932418 s: IPC: HLOS is ready !!! [MCU4_0] 16.953804 s: IPC: Init ... Done !!! [MCU4_0] 16.953844 s: APP: Syncing with 10 CPUs ... !!! [MCU4_0] 17.075311 s: APP: Syncing with 10 CPUs ... Done !!! [MCU4_0] 17.075347 s: REMOTE_SERVICE: Init ... !!! [MCU4_0] 17.077247 s: REMOTE_SERVICE: Init ... Done !!! [MCU4_0] 17.077293 s: FVID2: Init ... !!! [MCU4_0] 17.077353 s: FVID2: Init ... Done !!! [MCU4_0] 17.077380 s: VHWA: VPAC Init ... !!! [MCU4_0] 17.077403 s: SCICLIENT: Sciclient_pmSetModuleState module=400 state=2 [MCU4_0] 17.077599 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU4_0] 17.077634 s: VHWA: LDC Init ... !!! [MCU4_0] 17.083227 s: VHWA: LDC Init ... Done !!! [MCU4_0] 17.083264 s: VHWA: MSC Init ... !!! [MCU4_0] 17.096363 s: VHWA: MSC Init ... Done !!! [MCU4_0] 17.096400 s: VHWA: NF Init ... !!! [MCU4_0] 17.097851 s: VHWA: NF Init ... Done !!! [MCU4_0] 17.097884 s: VHWA: VISS Init ... !!! [MCU4_0] 17.108101 s: VHWA: VISS Init ... Done !!! [MCU4_0] 17.108142 s: VHWA: VPAC Init ... Done !!! [MCU4_0] 17.108178 s: VX_ZONE_INIT:Enabled [MCU4_0] 17.108203 s: VX_ZONE_ERROR:Enabled [MCU4_0] 17.108226 s: VX_ZONE_WARNING:Enabled [MCU4_0] 17.109093 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU4-0 [MCU4_0] 17.109286 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC2_NF [MCU4_0] 17.109471 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC2_LDC1 [MCU4_0] 17.109641 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC2_MSC1 [MCU4_0] 17.109807 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC2_MSC2 [MCU4_0] 17.110048 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target VPAC2_VISS1 [MCU4_0] 17.110094 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [MCU4_0] 17.110125 s: APP: OpenVX Target kernel init ... !!! [MCU4_0] 17.140478 s: APP: OpenVX Target kernel init ... Done !!! [MCU4_0] 17.140522 s: VISS REMOTE SERVICE: Init ... !!! [MCU4_0] 17.140584 s: VISS REMOTE SERVICE: Init ... Done !!! [MCU4_0] 17.140613 s: UDMA Copy: Init ... !!! [MCU4_0] 17.141763 s: UDMA Copy: Init ... Done !!! [MCU4_0] 17.141801 s: APP: Init ... Done !!! [MCU4_0] 17.141827 s: APP: Run ... !!! [MCU4_0] 17.141848 s: IPC: Starting echo test ... [MCU4_0] 17.146950 s: APP: Run ... Done !!! [MCU4_0] 17.148324 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[.] mcu3_1[.] mcu4_0[s] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU4_0] 17.148450 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[.] mcu3_1[P] mcu4_0[s] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU4_0] 17.148565 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[s] mcu4_1[.] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU4_0] 17.148769 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[s] mcu4_1[P] c7x_1[.] c7x_2[.] c7x_3[.] c7x_4[.] [MCU4_0] 17.148883 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[s] mcu4_1[P] c7x_1[P] c7x_2[.] c7x_3[.] c7x_4[.] [MCU4_0] 17.148993 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[s] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[.] c7x_4[.] [MCU4_0] 17.149102 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[s] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[.] [MCU4_0] 17.149212 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[s] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_0] 17.150029 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[s] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_1] 2.428618 s: CIO: Init ... Done !!! [MCU4_1] 2.428670 s: ### CPU Frequency = 1000000000 Hz [MCU4_1] 2.428703 s: CPU is running FreeRTOS [MCU4_1] 2.428724 s: APP: Init ... !!! [MCU4_1] 2.428746 s: SCICLIENT: Init ... !!! [MCU4_1] 2.428894 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [MCU4_1] 2.428930 s: SCICLIENT: DMSC FW revision 0x8 [MCU4_1] 2.428957 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU4_1] 2.428988 s: SCICLIENT: Init ... Done !!! [MCU4_1] 2.429011 s: MEM: Init ... !!! [MCU4_1] 2.429043 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ e5800000 of size 8388608 bytes !!! [MCU4_1] 2.429099 s: MEM: Init ... Done !!! [MCU4_1] 2.429121 s: IPC: Init ... !!! [MCU4_1] 2.429166 s: IPC: 11 CPUs participating in IPC !!! [MCU4_1] 2.429203 s: IPC: Waiting for HLOS to be ready ... !!! [MCU4_1] 17.053939 s: IPC: HLOS is ready !!! [MCU4_1] 17.075223 s: IPC: Init ... Done !!! [MCU4_1] 17.075272 s: APP: Syncing with 10 CPUs ... !!! [MCU4_1] 17.075311 s: APP: Syncing with 10 CPUs ... Done !!! [MCU4_1] 17.075342 s: REMOTE_SERVICE: Init ... !!! [MCU4_1] 17.077111 s: REMOTE_SERVICE: Init ... Done !!! [MCU4_1] 17.077159 s: VX_ZONE_INIT:Enabled [MCU4_1] 17.077182 s: VX_ZONE_ERROR:Enabled [MCU4_1] 17.077204 s: VX_ZONE_WARNING:Enabled [MCU4_1] 17.078145 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:66] Added target MCU4-1 [MCU4_1] 17.078191 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [MCU4_1] 17.078220 s: APP: OpenVX Target kernel init ... !!! [MCU4_1] 17.078253 s: APP: OpenVX Target kernel init ... Done !!! [MCU4_1] 17.078279 s: APP: Init ... Done !!! [MCU4_1] 17.078302 s: APP: Run ... !!! [MCU4_1] 17.078322 s: IPC: Starting echo test ... [MCU4_1] 17.083024 s: APP: Run ... Done !!! [MCU4_1] 17.084254 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[.] mcu4_0[x] mcu4_1[s] c7x_1[.] c7x_2[P] c7x_3[.] c7x_4[.] [MCU4_1] 17.084369 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[.] mcu4_0[x] mcu4_1[s] c7x_1[.] c7x_2[P] c7x_3[.] c7x_4[P] [MCU4_1] 17.084473 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[.] mcu4_0[x] mcu4_1[s] c7x_1[.] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_1] 17.084588 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[.] mcu4_0[x] mcu4_1[s] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_1] 17.084692 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[P] mcu4_0[x] mcu4_1[s] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_1] 17.084793 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[s] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_1] 17.094532 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[s] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_1] 17.147590 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[s] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [MCU4_1] 17.149108 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[s] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_1 ] 2.446917 s: CIO: Init ... Done !!! [C7x_1 ] 2.446935 s: ### CPU Frequency = 1000000000 Hz [C7x_1 ] 2.446949 s: CPU is running FreeRTOS [C7x_1 ] 2.446958 s: APP: Init ... !!! [C7x_1 ] 2.446966 s: SCICLIENT: Init ... !!! [C7x_1 ] 2.447092 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [C7x_1 ] 2.447111 s: SCICLIENT: DMSC FW revision 0x8 [C7x_1 ] 2.447123 s: SCICLIENT: DMSC FW ABI revision 3.1 [C7x_1 ] 2.447135 s: SCICLIENT: Init ... Done !!! [C7x_1 ] 2.447145 s: UDMA: Init ... !!! [C7x_1 ] 2.448129 s: UDMA: Init ... Done !!! [C7x_1 ] 2.448145 s: MEM: Init ... !!! [C7x_1 ] 2.448158 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 104000000 of size 67108864 bytes !!! [C7x_1 ] 2.448180 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 68000000 of size 3145728 bytes !!! [C7x_1 ] 2.448199 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 64800000 of size 458752 bytes !!! [C7x_1 ] 2.448218 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 64e00000 of size 16384 bytes !!! [C7x_1 ] 2.448237 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 10c000000 of size 67108864 bytes !!! [C7x_1 ] 2.448256 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000001) @ 100000000 of size 67108864 bytes !!! [C7x_1 ] 2.448276 s: MEM: Created heap (DDR_SCRATCH_NON_, id=6, flags=0x00000001) @ 108000000 of size 67108864 bytes !!! [C7x_1 ] 2.448295 s: MEM: Init ... Done !!! [C7x_1 ] 2.448304 s: IPC: Init ... !!! [C7x_1 ] 2.448323 s: IPC: 11 CPUs participating in IPC !!! [C7x_1 ] 2.448343 s: IPC: Waiting for HLOS to be ready ... !!! [C7x_1 ] 16.557075 s: IPC: HLOS is ready !!! [C7x_1 ] 16.562049 s: IPC: Init ... Done !!! [C7x_1 ] 16.562068 s: APP: Syncing with 10 CPUs ... !!! [C7x_1 ] 17.075313 s: APP: Syncing with 10 CPUs ... Done !!! [C7x_1 ] 17.075334 s: REMOTE_SERVICE: Init ... !!! [C7x_1 ] 17.075528 s: REMOTE_SERVICE: Init ... Done !!! [C7x_1 ] 17.075554 s: VX_ZONE_INIT:Enabled [C7x_1 ] 17.075568 s: VX_ZONE_ERROR:Enabled [C7x_1 ] 17.075580 s: VX_ZONE_WARNING:Enabled [C7x_1 ] 17.075815 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1 [C7x_1 ] 17.076032 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_2 [C7x_1 ] 17.076105 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_3 [C7x_1 ] 17.076169 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_4 [C7x_1 ] 17.076231 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_5 [C7x_1 ] 17.076293 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_6 [C7x_1 ] 17.076355 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_7 [C7x_1 ] 17.076419 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_8 [C7x_1 ] 17.076448 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [C7x_1 ] 17.076465 s: APP: OpenVX Target kernel init ... !!! [C7x_1 ] 17.077176 s: APP: OpenVX Target kernel init ... Done !!! [C7x_1 ] 17.077196 s: APP: Init ... Done !!! [C7x_1 ] 17.077207 s: APP: Run ... !!! [C7x_1 ] 17.077216 s: IPC: Starting echo test ... [C7x_1 ] 17.077341 s: APP: Run ... Done !!! [C7x_1 ] 17.080612 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[s] c7x_2[x] c7x_3[.] c7x_4[P] [C7x_1 ] 17.080720 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[s] c7x_2[x] c7x_3[P] c7x_4[P] [C7x_1 ] 17.082293 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[s] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_1 ] 17.083959 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[.] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[s] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_1 ] 17.084022 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[s] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_1 ] 17.084075 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[s] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_1 ] 17.094526 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[s] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_1 ] 17.147595 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[s] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_1 ] 17.149114 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[s] c7x_2[P] c7x_3[P] c7x_4[P] [C7x_2 ] 2.494250 s: CIO: Init ... Done !!! [C7x_2 ] 2.494268 s: ### CPU Frequency = 1000000000 Hz [C7x_2 ] 2.494281 s: CPU is running FreeRTOS [C7x_2 ] 2.494292 s: APP: Init ... !!! [C7x_2 ] 2.494301 s: SCICLIENT: Init ... !!! [C7x_2 ] 2.494439 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [C7x_2 ] 2.494458 s: SCICLIENT: DMSC FW revision 0x8 [C7x_2 ] 2.494471 s: SCICLIENT: DMSC FW ABI revision 3.1 [C7x_2 ] 2.494483 s: SCICLIENT: Init ... Done !!! [C7x_2 ] 2.494493 s: UDMA: Init ... !!! [C7x_2 ] 2.495475 s: UDMA: Init ... Done !!! [C7x_2 ] 2.495491 s: MEM: Init ... !!! [C7x_2 ] 2.495505 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 114000000 of size 67108864 bytes !!! [C7x_2 ] 2.495529 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 69000000 of size 3145728 bytes !!! [C7x_2 ] 2.495550 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 65800000 of size 458752 bytes !!! [C7x_2 ] 2.495570 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 65e00000 of size 16384 bytes !!! [C7x_2 ] 2.495589 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 11c000000 of size 67108864 bytes !!! [C7x_2 ] 2.495609 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000001) @ 110000000 of size 67108864 bytes !!! [C7x_2 ] 2.495629 s: MEM: Created heap (DDR_SCRATCH_NON_, id=6, flags=0x00000001) @ 118000000 of size 67108864 bytes !!! [C7x_2 ] 2.495649 s: MEM: Init ... Done !!! [C7x_2 ] 2.495660 s: IPC: Init ... !!! [C7x_2 ] 2.495679 s: IPC: 11 CPUs participating in IPC !!! [C7x_2 ] 2.495699 s: IPC: Waiting for HLOS to be ready ... !!! [C7x_2 ] 16.617109 s: IPC: HLOS is ready !!! [C7x_2 ] 16.622214 s: IPC: Init ... Done !!! [C7x_2 ] 16.622231 s: APP: Syncing with 10 CPUs ... !!! [C7x_2 ] 17.075313 s: APP: Syncing with 10 CPUs ... Done !!! [C7x_2 ] 17.075332 s: REMOTE_SERVICE: Init ... !!! [C7x_2 ] 17.075538 s: REMOTE_SERVICE: Init ... Done !!! [C7x_2 ] 17.075565 s: VX_ZONE_INIT:Enabled [C7x_2 ] 17.075579 s: VX_ZONE_ERROR:Enabled [C7x_2 ] 17.075591 s: VX_ZONE_WARNING:Enabled [C7x_2 ] 17.076524 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2 [C7x_2 ] 17.076595 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2_PRI_2 [C7x_2 ] 17.076660 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2_PRI_3 [C7x_2 ] 17.076723 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2_PRI_4 [C7x_2 ] 17.076786 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2_PRI_5 [C7x_2 ] 17.076849 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2_PRI_6 [C7x_2 ] 17.076911 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2_PRI_7 [C7x_2 ] 17.076978 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-2_PRI_8 [C7x_2 ] 17.077004 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [C7x_2 ] 17.077019 s: APP: OpenVX Target kernel init ... !!! [C7x_2 ] 17.079211 s: APP: OpenVX Target kernel init ... Done !!! [C7x_2 ] 17.079232 s: UDMA Copy: Init ... !!! [C7x_2 ] 17.081516 s: UDMA Copy: Init ... Done !!! [C7x_2 ] 17.081534 s: APP: Init ... Done !!! [C7x_2 ] 17.081545 s: APP: Run ... !!! [C7x_2 ] 17.081555 s: IPC: Starting echo test ... [C7x_2 ] 17.081672 s: APP: Run ... Done !!! [C7x_2 ] 17.082412 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[.] c7x_2[s] c7x_3[P] c7x_4[.] [C7x_2 ] 17.082479 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[.] [C7x_2 ] 17.082534 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[P] [C7x_2 ] 17.083988 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[.] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[P] [C7x_2 ] 17.084145 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[P] [C7x_2 ] 17.084209 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[P] [C7x_2 ] 17.094540 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[P] [C7x_2 ] 17.147606 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[P] [C7x_2 ] 17.149129 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[s] c7x_3[P] c7x_4[P] [C7x_3 ] 2.541626 s: CIO: Init ... Done !!! [C7x_3 ] 2.541643 s: ### CPU Frequency = 1000000000 Hz [C7x_3 ] 2.541658 s: CPU is running FreeRTOS [C7x_3 ] 2.541668 s: APP: Init ... !!! [C7x_3 ] 2.541677 s: SCICLIENT: Init ... !!! [C7x_3 ] 2.541813 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [C7x_3 ] 2.541832 s: SCICLIENT: DMSC FW revision 0x8 [C7x_3 ] 2.541845 s: SCICLIENT: DMSC FW ABI revision 3.1 [C7x_3 ] 2.541858 s: SCICLIENT: Init ... Done !!! [C7x_3 ] 2.541870 s: UDMA: Init ... !!! [C7x_3 ] 2.542888 s: UDMA: Init ... Done !!! [C7x_3 ] 2.542905 s: MEM: Init ... !!! [C7x_3 ] 2.542919 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 124000000 of size 67108864 bytes !!! [C7x_3 ] 2.542942 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 6a000000 of size 3145728 bytes !!! [C7x_3 ] 2.542961 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 66800000 of size 458752 bytes !!! [C7x_3 ] 2.542980 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 66e00000 of size 16384 bytes !!! [C7x_3 ] 2.542998 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 12c000000 of size 67108864 bytes !!! [C7x_3 ] 2.543019 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000001) @ 120000000 of size 67108864 bytes !!! [C7x_3 ] 2.543039 s: MEM: Created heap (DDR_SCRATCH_NON_, id=6, flags=0x00000001) @ 128000000 of size 67108864 bytes !!! [C7x_3 ] 2.543059 s: MEM: Init ... Done !!! [C7x_3 ] 2.543070 s: IPC: Init ... !!! [C7x_3 ] 2.543089 s: IPC: 11 CPUs participating in IPC !!! [C7x_3 ] 2.543109 s: IPC: Waiting for HLOS to be ready ... !!! [C7x_3 ] 16.660280 s: IPC: HLOS is ready !!! [C7x_3 ] 16.664971 s: IPC: Init ... Done !!! [C7x_3 ] 16.664990 s: APP: Syncing with 10 CPUs ... !!! [C7x_3 ] 17.075314 s: APP: Syncing with 10 CPUs ... Done !!! [C7x_3 ] 17.075336 s: REMOTE_SERVICE: Init ... !!! [C7x_3 ] 17.075555 s: REMOTE_SERVICE: Init ... Done !!! [C7x_3 ] 17.075578 s: VX_ZONE_INIT:Enabled [C7x_3 ] 17.075592 s: VX_ZONE_ERROR:Enabled [C7x_3 ] 17.075605 s: VX_ZONE_WARNING:Enabled [C7x_3 ] 17.075900 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3 [C7x_3 ] 17.076102 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3_PRI_2 [C7x_3 ] 17.076181 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3_PRI_3 [C7x_3 ] 17.076257 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3_PRI_4 [C7x_3 ] 17.076332 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3_PRI_5 [C7x_3 ] 17.076409 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3_PRI_6 [C7x_3 ] 17.076492 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3_PRI_7 [C7x_3 ] 17.076581 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-3_PRI_8 [C7x_3 ] 17.076612 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [C7x_3 ] 17.076627 s: APP: OpenVX Target kernel init ... !!! [C7x_3 ] 17.077410 s: APP: OpenVX Target kernel init ... Done !!! [C7x_3 ] 17.077429 s: UDMA Copy: Init ... !!! [C7x_3 ] 17.079827 s: UDMA Copy: Init ... Done !!! [C7x_3 ] 17.079845 s: APP: Init ... Done !!! [C7x_3 ] 17.079861 s: APP: Run ... !!! [C7x_3 ] 17.079872 s: IPC: Starting echo test ... [C7x_3 ] 17.080030 s: APP: Run ... Done !!! [C7x_3 ] 17.080771 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[.] c7x_2[x] c7x_3[s] c7x_4[P] [C7x_3 ] 17.080833 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[P] c7x_2[x] c7x_3[s] c7x_4[P] [C7x_3 ] 17.082382 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[P] c7x_2[P] c7x_3[s] c7x_4[P] [C7x_3 ] 17.084008 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[.] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[s] c7x_4[P] [C7x_3 ] 17.084161 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[s] c7x_4[P] [C7x_3 ] 17.084222 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[s] c7x_4[P] [C7x_3 ] 17.094548 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[s] c7x_4[P] [C7x_3 ] 17.147619 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[s] c7x_4[P] [C7x_3 ] 17.149137 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[s] c7x_4[P] [C7x_4 ] 2.590969 s: CIO: Init ... Done !!! [C7x_4 ] 2.590985 s: ### CPU Frequency = 1000000000 Hz [C7x_4 ] 2.590999 s: CPU is running FreeRTOS [C7x_4 ] 2.591009 s: APP: Init ... !!! [C7x_4 ] 2.591018 s: SCICLIENT: Init ... !!! [C7x_4 ] 2.591154 s: SCICLIENT: DMSC FW version [8.5.2--v08.05.02 (Chill Capybar] [C7x_4 ] 2.591170 s: SCICLIENT: DMSC FW revision 0x8 [C7x_4 ] 2.591182 s: SCICLIENT: DMSC FW ABI revision 3.1 [C7x_4 ] 2.591194 s: SCICLIENT: Init ... Done !!! [C7x_4 ] 2.591205 s: UDMA: Init ... !!! [C7x_4 ] 2.592204 s: UDMA: Init ... Done !!! [C7x_4 ] 2.592217 s: MEM: Init ... !!! [C7x_4 ] 2.592231 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ 134000000 of size 67108864 bytes !!! [C7x_4 ] 2.592253 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 6b000000 of size 3145728 bytes !!! [C7x_4 ] 2.592273 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 67800000 of size 458752 bytes !!! [C7x_4 ] 2.592292 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 67e00000 of size 16384 bytes !!! [C7x_4 ] 2.592310 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ 13c000000 of size 67108864 bytes !!! [C7x_4 ] 2.592330 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000001) @ 130000000 of size 67108864 bytes !!! [C7x_4 ] 2.592350 s: MEM: Created heap (DDR_SCRATCH_NON_, id=6, flags=0x00000001) @ 138000000 of size 67108864 bytes !!! [C7x_4 ] 2.592370 s: MEM: Init ... Done !!! [C7x_4 ] 2.592379 s: IPC: Init ... !!! [C7x_4 ] 2.592396 s: IPC: 11 CPUs participating in IPC !!! [C7x_4 ] 2.592414 s: IPC: Waiting for HLOS to be ready ... !!! [C7x_4 ] 16.711771 s: IPC: HLOS is ready !!! [C7x_4 ] 16.715814 s: IPC: Init ... Done !!! [C7x_4 ] 16.715831 s: APP: Syncing with 10 CPUs ... !!! [C7x_4 ] 17.075314 s: APP: Syncing with 10 CPUs ... Done !!! [C7x_4 ] 17.075335 s: REMOTE_SERVICE: Init ... !!! [C7x_4 ] 17.075562 s: REMOTE_SERVICE: Init ... Done !!! [C7x_4 ] 17.075587 s: VX_ZONE_INIT:Enabled [C7x_4 ] 17.075603 s: VX_ZONE_ERROR:Enabled [C7x_4 ] 17.075618 s: VX_ZONE_WARNING:Enabled [C7x_4 ] 17.075929 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4 [C7x_4 ] 17.076122 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4_PRI_2 [C7x_4 ] 17.076198 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4_PRI_3 [C7x_4 ] 17.076273 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4_PRI_4 [C7x_4 ] 17.076350 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4_PRI_5 [C7x_4 ] 17.076425 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4_PRI_6 [C7x_4 ] 17.076498 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4_PRI_7 [C7x_4 ] 17.076575 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-4_PRI_8 [C7x_4 ] 17.076599 s: VX_ZONE_INIT:[tivxInitLocal:145] Initialization Done !!! [C7x_4 ] 17.076613 s: APP: OpenVX Target kernel init ... !!! [C7x_4 ] 17.077412 s: APP: OpenVX Target kernel init ... Done !!! [C7x_4 ] 17.077434 s: UDMA Copy: Init ... !!! [C7x_4 ] 17.079760 s: UDMA Copy: Init ... Done !!! [C7x_4 ] 17.079778 s: APP: Init ... Done !!! [C7x_4 ] 17.079791 s: APP: Run ... !!! [C7x_4 ] 17.079802 s: IPC: Starting echo test ... [C7x_4 ] 17.079943 s: APP: Run ... Done !!! [C7x_4 ] 17.080602 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[P] c7x_2[x] c7x_3[.] c7x_4[s] [C7x_4 ] 17.080794 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[P] c7x_2[x] c7x_3[P] c7x_4[s] [C7x_4 ] 17.082400 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[x] mcu3_1[x] mcu4_0[x] mcu4_1[x] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[s] [C7x_4 ] 17.083935 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[.] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[s] [C7x_4 ] 17.084204 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[.] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[s] [C7x_4 ] 17.084265 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[s] [C7x_4 ] 17.094564 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[x] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[s] [C7x_4 ] 17.147632 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[s] [C7x_4 ] 17.149149 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] mcu3_0[P] mcu3_1[P] mcu4_0[P] mcu4_1[P] c7x_1[P] c7x_2[P] c7x_3[P] c7x_4[s] [MCU2_0] 78.654136 s: ImageSensor_RemoteServiceHandler: IM_SENSOR_CMD_ENUMERATE [MCU2_0] 99.093113 s: ImageSensor_RemoteServiceHandler: IM_SENSOR_CMD_QUERY [MCU2_0] 99.093148 s: Received Query for OVX3CF-MAX96717_MARS [MCU2_0] 99.093576 s: ImageSensor_RemoteServiceHandler: IM_SENSOR_CMD_PWRON [MCU2_0] 99.093609 s: IM_SENSOR_CMD_PWRON : channel_mask = 0x10 [MCU2_0] 99.094250 s: ImageSensor_RemoteServiceHandler: IM_SENSOR_CMD_CONFIG [MCU2_0] 99.094284 s: Application requested features = 0x158 [MCU2_0] [MCU2_0] 99.094315 s: channel_mask = 0x10 [MCU2_0] [MCU2_0] 99.094347 s: Configuring camera on csi --1--, channel --0-- [MCU2_0] 99.094384 s: Configuring camera real id --4-- [MCU2_0] 99.094427 s: OVX3CF_MAXIM i2cInstId: 5 [MCU2_0] 99.094465 s: max96712_cfgScript : max96712 I2cAddr = 0x6b [MCU2_0] 99.094533 s: [max96712_cfgScript] :rawRegVal: 0x0013 0x75 [MCU2_0] 99.094624 s: Error writing 0x75 to MAX96712 register 0x13 [MCU2_0] 99.094664 s: MAX96712: Reg Write Failed for regAddr 13 [MCU2_0] 99.094691 s: End of MAX96712 config [MCU2_0] 99.128729 s: src/fvid2_drvMgr.c @ Line 768: [MCU2_0] 99.128765 s: EALLOC: Invalid driver ID!! [MCU2_0] 99.128802 s: VX_ZONE_ERROR:[tivxDisplayCreate:545] DISPLAY: ERROR: Display Create Failed! [MCU2_0] 99.129567 s: ========================================================== [MCU2_0] 99.129623 s: Capture Status: Instance|0 [MCU2_0] 99.129649 s: ========================================================== [MCU2_0] 99.129687 s: overflowCount: 0 [MCU2_0] 99.129716 s: spuriousUdmaIntrCount: 0 [MCU2_0] 99.129746 s: frontFIFOOvflCount: 0 [MCU2_0] 99.129773 s: crcCount: 0 [MCU2_0] 99.129798 s: eccCount: 0 [MCU2_0] 99.129824 s: correctedEccCount: 0 [MCU2_0] 99.129853 s: dataIdErrorCount: 0 [MCU2_0] 99.129882 s: invalidAccessCount: 0 [MCU2_0] 99.129910 s: invalidSpCount: 0 [MCU2_0] 99.129943 s: strmFIFOOvflCount[0]: 0 [MCU2_0] 99.129976 s: strmFIFOOvflCount[1]: 0 [MCU2_0] 99.130001 s: Channel Num | Frame Queue Count | Frame De-queue Count | Frame Drop Count | Error Frame Count | [MCU2_0] 99.130252 s: ========================================================== [MCU2_0] 99.130309 s: Capture Status: Instance|1 [MCU2_0] 99.130337 s: ========================================================== [MCU2_0] 99.130378 s: overflowCount: 0 [MCU2_0] 99.130409 s: spuriousUdmaIntrCount: 0 [MCU2_0] 99.130441 s: frontFIFOOvflCount: 0 [MCU2_0] 99.130470 s: crcCount: 0 [MCU2_0] 99.130497 s: eccCount: 0 [MCU2_0] 99.130524 s: correctedEccCount: 0 [MCU2_0] 99.130555 s: dataIdErrorCount: 0 [MCU2_0] 99.130585 s: invalidAccessCount: 0 [MCU2_0] 99.130615 s: invalidSpCount: 0 [MCU2_0] 99.130651 s: strmFIFOOvflCount[0]: 0 [MCU2_0] 99.130687 s: strmFIFOOvflCount[1]: 0 [MCU2_0] 99.130714 s: Channel Num | Frame Queue Count | Frame De-queue Count | Frame Drop Count | Error Frame Count | [MCU2_0] 99.130783 s: 0 | 0 | 0 | 0 | 0 | [MCU2_0] 99.133832 s: ImageSensor_RemoteServiceHandler: IM_SENSOR_CMD_STREAM_ON [MCU2_0] 99.133890 s: IM_SENSOR_CMD_STREAM_ON: channel_mask = 0x10 [MCU2_0] 99.133926 s: Starting camera on csi --1--, channel --0-- [MCU2_0] 99.133965 s: HJX Stream On: Sensor I2c address = 0x36 [MCU2_0] 99.134018 s: HJX Stream On: Sensor I2c address = 0x36 [MCU2_0] 99.134093 s: Error writing to register 0x100 [MCU2_0] [MCU2_0] 99.134151 s: Error : Failed to start sensor at csi 1, channel Id 0

diff --git a/../vhtest/ti-processor-sdk-rtos-j784s4-evm-08_05_00_11/pdk_j784s4_08_05_00_37/packages/ti/board/src/j784s4_evm/J784S4_pinmux_data.c b/./pdk_j784s4_08_05_00_37/packages/ti/board/src/j784s4_evm/J784S4_pinmux_data.c

index 2c4cb58..16980e6 100644

--- a/../vhtest/ti-processor-sdk-rtos-j784s4-evm-08_05_00_11/pdk_j784s4_08_05_00_37/packages/ti/board/src/j784s4_evm/J784S4_pinmux_data.c

+++ b/./pdk_j784s4_08_05_00_37/packages/ti/board/src/j784s4_evm/J784S4_pinmux_data.c

@@ -187,6 +187,20 @@ static pinmuxModuleCfg_t gGpio_vddshv2PinCfg[] =

{PINMUX_END}

};

+static pinmuxPerCfg_t gI2c6PinCfg[] =

+{

+ /* MyI2C5 -> I2C6_SCL -> AN37 */

+ {

+ PIN_TIMER_IO1, PIN_MODE(13) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyI2C6 -> I2C6_SDA -> AR38 */

+ {

+ PIN_TIMER_IO0, PIN_MODE(13) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ {PINMUX_END}

+};

static pinmuxPerCfg_t gI2c4PinCfg[] =

{

@@ -205,14 +219,14 @@ static pinmuxPerCfg_t gI2c4PinCfg[] =

static pinmuxPerCfg_t gI2c5PinCfg[] =

{

- /* MyI2C5 -> I2C5_SCL -> AG34 */

+ /* MyI2C5 -> I2C5_SCL -> AC33 */

{

- PIN_MCAN15_TX, PIN_MODE(8) | \

+ PIN_MCAN2_TX, PIN_MODE(13) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyI2C5 -> I2C5_SDA -> AK36 */

+ /* MyI2C5 -> I2C5_SDA -> AH37 */

{

- PIN_MCAN14_RX, PIN_MODE(8) | \

+ PIN_MCAN2_RX, PIN_MODE(13) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

{PINMUX_END}

@@ -265,6 +279,7 @@ static pinmuxPerCfg_t gI2c0PinCfg[] =

static pinmuxModuleCfg_t gI2cPinCfg[] =

{

+ {6, TRUE, gI2c6PinCfg},

{4, TRUE, gI2c4PinCfg},

{5, TRUE, gI2c5PinCfg},

{3, TRUE, gI2c3PinCfg},

@@ -792,10 +807,10 @@ static pinmuxPerCfg_t gMmcsd1PinCfg[] =

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

/* MyMMCSD1 -> MMC1_SDCD -> AR38 */

- {

- PIN_TIMER_IO0, PIN_MODE(8) | \

- ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

- },

+ // {

+ // PIN_TIMER_IO0, PIN_MODE(8) | \

+ // ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ // },

/* MyMMC1 -> MMC1_CLKLB */

{

PIN_MMC1_CLKLB, PIN_MODE(0) | \

@@ -900,20 +915,20 @@ static pinmuxPerCfg_t gUart6PinCfg[] =

{PINMUX_END}

};

-static pinmuxPerCfg_t gUart3PinCfg[] =

-{

- /* MyUART3 -> UART3_RXD -> AC33 */

- {

- PIN_MCAN2_TX, PIN_MODE(11) | \

- ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

- },

- /* MyUART3 -> UART3_TXD -> AH37 */

- {

- PIN_MCAN2_RX, PIN_MODE(11) | \

- ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

- },

- {PINMUX_END}

-};

+// static pinmuxPerCfg_t gUart3PinCfg[] =

+// {

+// /* MyUART3 -> UART3_RXD -> AC33 */

+// {

+// PIN_MCAN2_TX, PIN_MODE(11) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyUART3 -> UART3_TXD -> AH37 */

+// {

+// PIN_MCAN2_RX, PIN_MODE(11) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// {PINMUX_END}

+// };

static pinmuxPerCfg_t gUart2PinCfg[] =

{

@@ -960,28 +975,28 @@ static pinmuxModuleCfg_t gUartPinCfg[] =

{5, TRUE, gUart5PinCfg},

{9, TRUE, gUart9PinCfg},

{6, TRUE, gUart6PinCfg},

- {3, TRUE, gUart3PinCfg},

+ // {3, TRUE, gUart3PinCfg},

{2, TRUE, gUart2PinCfg},

{8, TRUE, gUart8PinCfg},

{PINMUX_END}

};

-static pinmuxPerCfg_t gUsb0PinCfg[] =

-{

- /* MyUSB0 -> USB0_DRVVBUS -> AN37 */

- {

- PIN_TIMER_IO1, PIN_MODE(6) | \

- ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

- },

- {PINMUX_END}

-};

+// static pinmuxPerCfg_t gUsb0PinCfg[] =

+// {

+// /* MyUSB0 -> USB0_DRVVBUS -> AN37 */

+// {

+// PIN_TIMER_IO1, PIN_MODE(6) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// {PINMUX_END}

+// };

-static pinmuxModuleCfg_t gUsbPinCfg[] =

-{

- {0, TRUE, gUsb0PinCfg},

- {PINMUX_END}

-};

+// static pinmuxModuleCfg_t gUsbPinCfg[] =

+// {

+// {0, TRUE, gUsb0PinCfg},

+// {PINMUX_END}

+// };

static pinmuxPerCfg_t gWkup_gpio_vddshv0_mcu0PinCfg[] =

@@ -1241,7 +1256,7 @@ pinmuxBoardCfg_t gJ784S4_MainPinmuxData[] =

{8, gSystem_vddshv0PinCfg},

{9, gSystem_vddshv2PinCfg},

{10, gUartPinCfg},

- {11, gUsbPinCfg},

+ // {11, gUsbPinCfg},

{PINMUX_END}

};

diff --git a/../vhtest/ti-processor-sdk-rtos-j784s4-evm-08_05_00_11/vision_apps/utils/misc/src/app_pinmux_j784s4.c b/./vision_apps/utils/misc/src/app_pinmux_j784s4.c

index 0fefd39..2267cb9 100755

--- a/../vhtest/ti-processor-sdk-rtos-j784s4-evm-08_05_00_11/vision_apps/utils/misc/src/app_pinmux_j784s4.c

+++ b/./vision_apps/utils/misc/src/app_pinmux_j784s4.c

@@ -110,16 +110,46 @@ static pinmuxModuleCfg_t gDispPinCfg[] =

{PINMUX_END}

};

+static pinmuxPerCfg_t gI2c6PinCfg[] =

+{

+ /* MyI2C5 -> I2C6_SCL -> AN37 */

+ {

+ PIN_TIMER_IO1, PIN_MODE(13) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyI2C6 -> I2C6_SDA -> AR38 */

+ {

+ PIN_TIMER_IO0, PIN_MODE(13) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ {PINMUX_END}

+};

+

static pinmuxPerCfg_t gI2c5PinCfg[] =

{

- /* MyI2C5 -> I2C5_SCL -> AG34 */

+ /* MyI2C5 -> I2C5_SCL -> AC33 */

+ {

+ PIN_MCAN2_TX, PIN_MODE(13) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyI2C5 -> I2C5_SDA -> AH37 */

+ {

+ PIN_MCAN2_RX, PIN_MODE(13) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ {PINMUX_END}

+};

+

+static pinmuxPerCfg_t gI2c1PinCfg[] =

+{

+ /* MyI2C1 -> I2C1_SCL -> AD36 */

{

- PIN_MCAN15_TX, PIN_MODE(8) | \

+ PIN_ECAP0_IN_APWM_OUT, PIN_MODE(13) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyI2C5 -> I2C5_SDA -> AK36 */

+ /* MyI2C1 -> I2C1_SDA -> AJ32 */

{

- PIN_MCAN14_RX, PIN_MODE(8) | \

+ PIN_EXT_REFCLK1, PIN_MODE(13) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

{PINMUX_END}

@@ -127,7 +157,9 @@ static pinmuxPerCfg_t gI2c5PinCfg[] =

static pinmuxModuleCfg_t gCaptPinCfg[] =

{

- {0, TRUE, gI2c5PinCfg},

+ {6, TRUE, gI2c6PinCfg},

+ {5, TRUE, gI2c5PinCfg},

+ {1, TRUE, gI2c1PinCfg},

{PINMUX_END}

};