My customer is developing the interface logic of FPGA for AM5726 with GPMC.

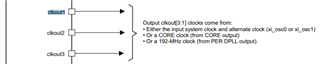

FPGA uses clkout1 output by AM5726 as its operating clock.

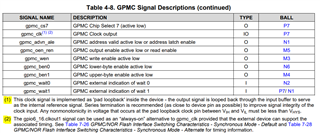

When GPMC_CLK_MUXMODE of CTRL_CORE_PAD_GPMC_CLK

[3:0] is set to 0x2

1. They would like to know the synchronization relationship and phase relationship between clkout1 and GPMC_CLK.

2. Which clock source is clkout1 generated from?

The above information is required for timing design on the FPGA side.

Best regards

T. Sakuma