Other Parts Discussed in Thread: SYSBIOS

Hi~

Environment Description:

DSP model: TMS320C6678

DDR3: DDR3 is connected to 4Gb/4bit DDR16 surface-mount memory particles, designed as a single rank

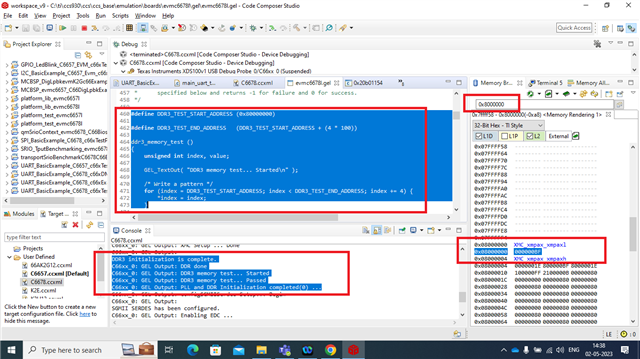

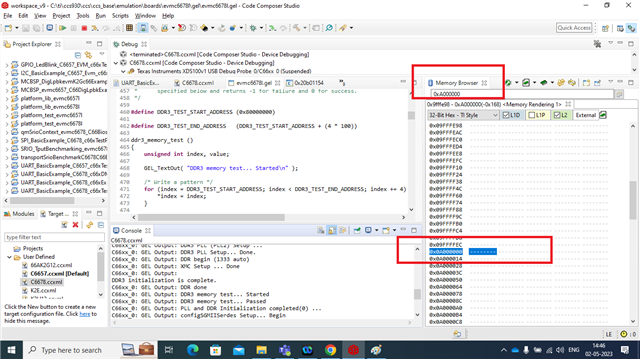

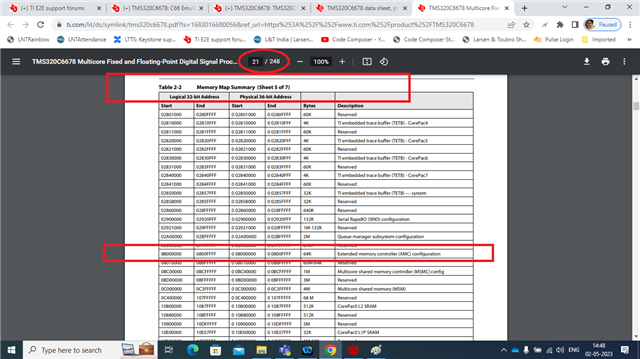

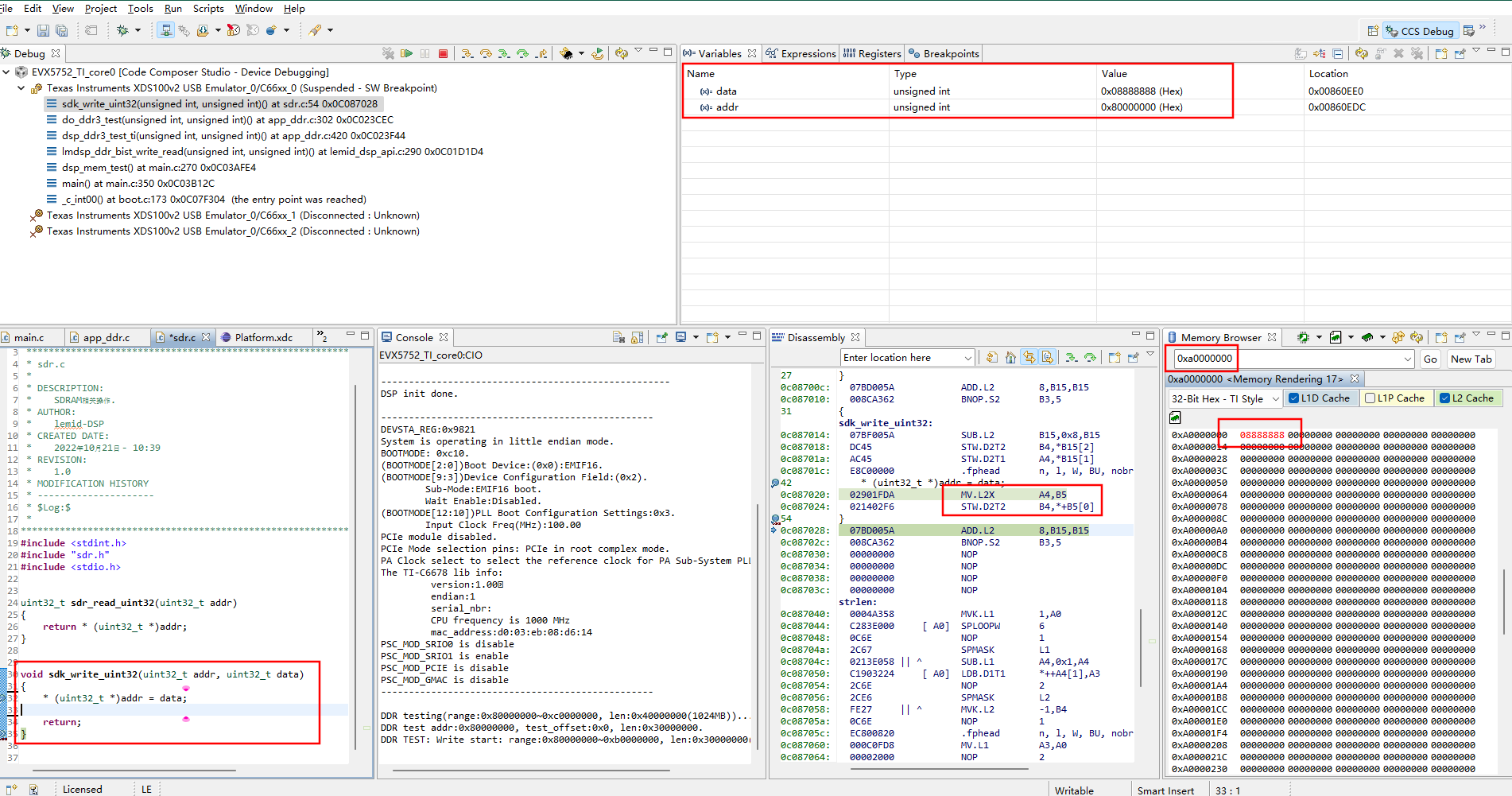

When I use the C6678 DSP to debug DDR, I have a phenomenon that I don't understand: when writing a 0-byte of data to the address 8000x0000 4, I find that the data in the 0xA000 0000, 0xC000 0000 and other addresses also appears.

Here is my DDR test code:

uint32_t sdr_read_uint32(uint32_t addr)

{

return * (uint32_t *)addr;

}

void ddr_test()

{

sdk_write_uint32(0x80000000, 0x01111111*0x8);

sdk_write_uint32(0x90000000, 0x01111111*0x9);

sdk_write_uint32(0xa0000000, 0x01111111*0xa);

sdk_write_uint32(0xb0000000, 0x01111111*0xb);

sdk_write_uint32(0xc0000000, 0x01111111*0xc);

sdk_write_uint32(0xd0000000, 0x01111111*0xd);

sdk_write_uint32(0xe0000000, 0x01111111*0xe);

sdk_write_uint32(0xf0000000, 0x01111111*0xf);

return;

}

When data is written to 0x8000 0000 0x0888 8888, it is found that the contents of 0xA000 0000, 0xC000 0000, 0xE000 0000 addresses are also written as 0x0888 8888. As shown in the following figure:

I analyzed this problem as follows:

1. Through the analysis and compilation, the destination address of STW is also 0x8000 0000, not 0xA000 0000. So it doesn't feel like a logical problem with the software;

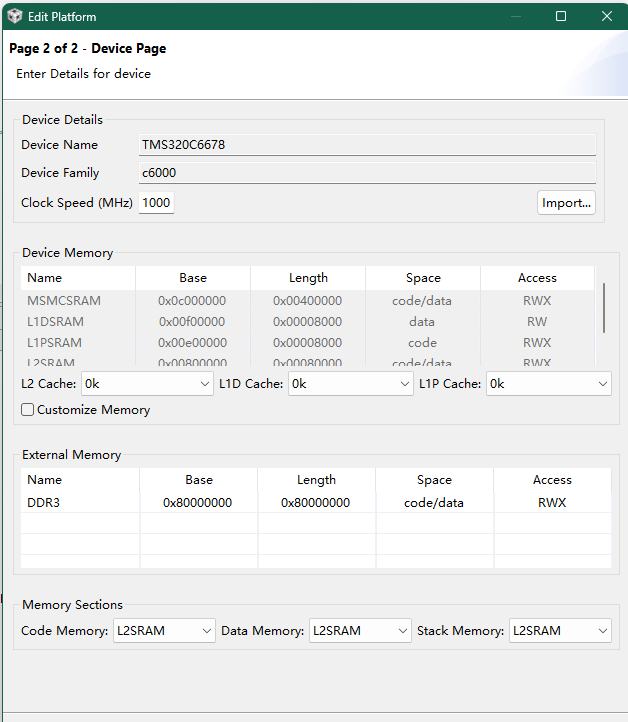

2. I also suspected that memory sharing that may be multi-core may be affected, but after setting DDR3 of External Memory in my platform to the following configuration, there is still this problem.

3. Suspecting that it may be related to multicore, I changed the multicore configuration in my .cfg file to single core, the corresponding configuration file is as follows, or does this issue exist:

var BIOS = xdc.useModule('ti.sysbios.BIOS');

var Task = xdc.useModule('ti.sysbios.knl.Task');

var cslSettings = xdc.useModule ('ti.csl.Settings');

var Cppi = xdc.loadPackage('ti.drv.cppi');

var Qmss = xdc.loadPackage('ti.drv.qmss');

var Srio = xdc.loadPackage('ti.drv.srio');

var HWI = xdc.useModule ('ti.sysbios.hal.Hwi');

var CPINTC = xdc.useModule('ti.sysbios.family.c66.tci66xx.CpIntc');

var ECM = xdc.useModule('ti.sysbios.family.c64p.EventCombiner');

var Pa = xdc.useModule('ti.drv.pa.Settings');

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

var Mailbox = xdc.useModule('ti.sysbios.knl.Mailbox');

var Memory = xdc.useModule('xdc.runtime.Memory');

var Notify = xdc.useModule('ti.sdo.ipc.Notify');

var Ipc = xdc.useModule('ti.sdo.ipc.Ipc');

//多核相关

var MultiProc = xdc.useModule('ti.sdo.utils.MultiProc');

//MultiProc.numProcessors = 8;

//MultiProc.setConfig(null, ["CORE0", "CORE1", "CORE2", "CORE3","CORE4","CORE5","CORE6","CORE7"]);

MultiProc.numProcessors = 1;

//MultiProc.setConfig(null, ["CORE0", "CORE1", "CORE2"]);

MultiProc.setConfig(null, ["CORE0"]);

/* Required if using System_printf to output on the console */

var System = xdc.useModule('xdc.runtime.System');

var SysStd = xdc.useModule('xdc.runtime.SysStd');

System.SupportProxy = SysStd;

var PlatformLib = xdc.loadPackage('ti.platform.evmc6678l');

var NdkTransport = xdc.loadPackage('ti.transport.ndk');

ECM.eventGroupHwiNum[0] = 7;

ECM.eventGroupHwiNum[1] = 8;

ECM.eventGroupHwiNum[2] = 9;

ECM.eventGroupHwiNum[3] = 10;

//面两条6678初始化被RYB注释掉,初始化移至MAIN函数中执行

//Startup = xdc.useModule('xdc.runtime.Startup');

//Startup.firstFxns.$add('&C6678_init');

var Global = xdc.useModule('ti.ndk.config.Global');

Global.enableCodeGeneration = false;

//BIOS.heapSize = 0x10000;

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var heapMemParams = new HeapMem.Params();

heapMemParams.size = 0x200000;

heapMemParams.sectionName = "systemHeap";

Program.global.heap0 = HeapMem.create(heapMemParams);

/* This is the default memory heap. */

Memory.defaultHeapInstance = Program.global.heap0;

/*

** Create the stack Thread Task for our application.

*/

var Exception = xdc.useModule('ti.sysbios.family.c64p.Exception');

Exception.enablePrint = true;

/* To avoid wasting shared memory for Notify and MessageQ transports */

for (var i = 0; i < MultiProc.numProcessors; i++) {

Ipc.setEntryMeta({

remoteProcId: i,

setupMessageQ: false,

});

}

/* Synchronize all processors (this will be done in Ipc_start) */

Ipc.procSync = Ipc.ProcSync_ALL;

/*

* Need to define the shared region. The IPC modules use this

* to make portable pointers. All processors need to add this

* call with their base address of the shared memory region.

* If the processor cannot access the memory, do not add it.

*/

var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion');

SharedRegion.setEntryMeta(0,

{ base: 0x0C180000,

len: 0x00080000,

ownerProcId: 0,

isValid: true,

name: "MSMCSRAM_IPC",

});

Program.sectMap[".srioSharedMem"] = "L2SRAM"; //DDR3

Program.sectMap[".boot_sect"] = "L2SRAM";

Program.sectMap["sharedL2"] = "MSMCSRAM";

Program.sectMap["systemHeap"] = "MSMCSRAM";

Program.sectMap[".sysmem"] = "MSMCSRAM";

Program.sectMap[".args"] = "MSMCSRAM";

Program.sectMap[".cio"] = "MSMCSRAM";

Program.sectMap[".far"] = "MSMCSRAM";

Program.sectMap[".rodata"] = "MSMCSRAM";

Program.sectMap[".neardata"] = "MSMCSRAM";

Program.sectMap[".cppi"] = "MSMCSRAM";

Program.sectMap[".init_array"] = "MSMCSRAM";

Program.sectMap[".qmss"] = "MSMCSRAM";

Program.sectMap[".cinit"] = "MSMCSRAM";

Program.sectMap[".bss"] = "MSMCSRAM";

Program.sectMap[".const"] = "MSMCSRAM";

Program.sectMap[".text"] = "MSMCSRAM";

Program.sectMap[".code"] = "MSMCSRAM";

Program.sectMap[".switch"] = "MSMCSRAM";

Program.sectMap[".data"] = "MSMCSRAM";

Program.sectMap[".fardata"] = "MSMCSRAM";

Program.sectMap[".args"] = "MSMCSRAM";

Program.sectMap[".cio"] = "MSMCSRAM";

Program.sectMap[".vecs"] = "MSMCSRAM";

Program.sectMap["platform_lib"] = "MSMCSRAM";

Program.sectMap["TI_platform_lib"] = "MSMCSRAM";

Program.sectMap[".far:taskStackSection"] = "MSMCSRAM";

Program.sectMap[".stack"] = "L2SRAM";

Program.sectMap[".nimu_eth_ll2"] = "L2SRAM";

Program.sectMap[".resmgr_memregion"] = {loadSegment: "L2SRAM", loadAlign:128}; /* QMSS descriptors region */

Program.sectMap[".resmgr_handles"] = {loadSegment: "L2SRAM", loadAlign:16}; /* CPPI/QMSS/PA Handles */

Program.sectMap[".resmgr_pa"] = {loadSegment: "L2SRAM", loadAlign:8}; /* PA Memory */

Program.sectMap[".far:IMAGEDATA"] = {loadSegment: "L2SRAM", loadAlign: 8};

Program.sectMap[".far:NDK_OBJMEM"] = {loadSegment: "L2SRAM", loadAlign: 8};

Program.sectMap[".far:NDK_PACKETMEM"] = {loadSegment: "L2SRAM", loadAlign: 128};

Program.sectMap[".msm_user"] = "MSMCSRAM";

Program.sectMap[".NDKDESC"] = "MSMCSRAM"; //MSMCSRAM

Program.sectMap[".csl_vect"] = "MSMCSRAM"; //MSMCSRAM

/* self defined */

Program.sectMap[".revcomad"] ="MSMCSRAM";

Program.sectMap[".msmc_slave_addr"] ="MSMCSRAM";

Program.sectMap[".data_ddr"] ="DDR3";

Please help take a look, what is the reason for this phenomenon?

Thank you!