Other Parts Discussed in Thread: SYSCONFIG, TLV320AIC3106

Hi AM62x support,

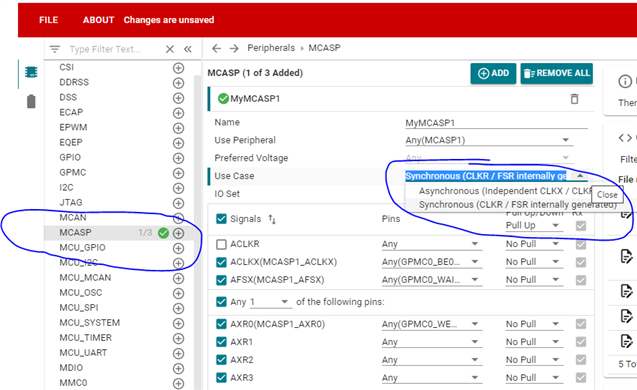

Our customer is trying to configure the GPIO multiplexer on the AM62 to enable the McASP. They've tried two methods:

- Using CCS to configure U-Boot. Led to an error importing the .sysconfig file from the SDK.

- Use Sysconfig, but they get an empty configuration file, so they couldn't setup the rest of the board for the project.

They're working on the EVM.

Can you send the right starting point here? What document should they be following for this process.

Thanks,

Darren