Hi Jacinto Champ !

Can you please check if USB circuit was designed for appropriate working ?

To help you with the translation in the attached picture,

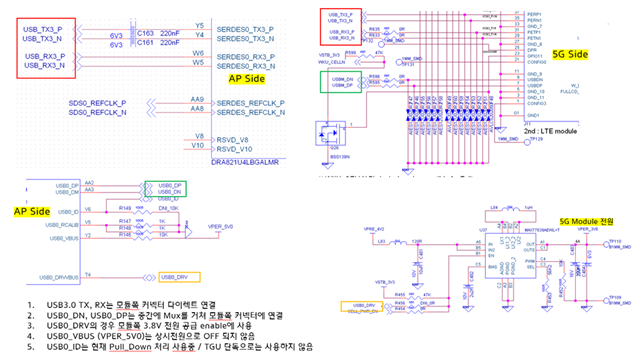

1. USB 3.0 TX, RX connected directly to the connector on the 5G module.

2. USB0_DN and USB0_DP are connected to the module connector via MUX in the middle

3. The USB0_DRV is used as the 3.8V power supply enable signal for the 5G module.

4. USB0_VBUS (VPER_5V0) is not turned off at all times.

5. USB0_ID is currently processed by Pull_Down