Part Number: AM6412

Hello,

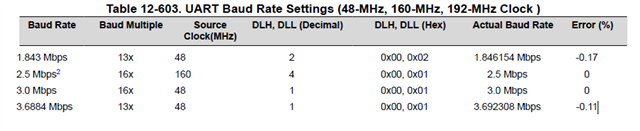

We're seeing some bytes got dropped when talking with 3Mbps baud rate with another chip. AM6412 is running Linux from SDK8.04

A SN74AVC4T245RSV is used between these 2 chips to meet the requirement of maximum capacitor at Rx side.

The communication protocol is always in a 16B frame. we're seeing:

1. from AM6412 to the other chip, everything looks good. No packet loss is observed.

2. from the other chip to AM6412, there's a chance of lost 1 byte at the beginning of a frame: about 0.1% frames got 1st byte loss, and ~0.02% 2nd byte loss.

Linux kernel driver is not reporting buffer overrun.

There's almost no bytes loss if they're running at 1Mbps baud rate.

Please advise what we need to do to address this issue.

Thanks a lot,

Leon