Hello,

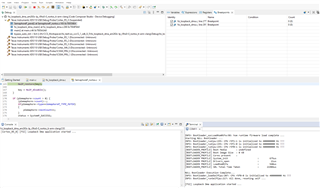

I'm testing the FSI-interface in DMA-mode. For this, I've imported the example (FSI in loopbackmode, DMA, nortos) from SDK-version 8.5.24. We use the Code Composer Studio version 12.2.

The example runs correct, if do debugging in single step mode. The data are transmitted and received correctly.

But if I run the example from main function start to a breakpoint (no single step operation) after the semaphores, waiting for the receive of the looped backed data from FSI, the software is looping endless in the semaphore, waiting for the RX of FSI.

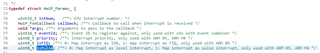

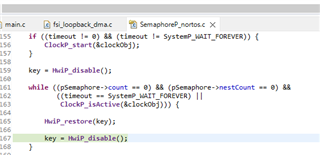

The breakpoint is set here:

The software is hanging in the RX semaphore:

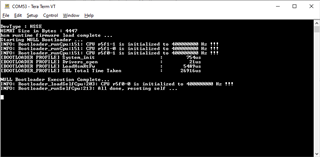

We tried the example also with SBL from the external flash. In this constellation, the example is running without any problems (in release and debug compile).

A collegue of me has the problem on his evaluation board also.

The problem is 100% reproducable.

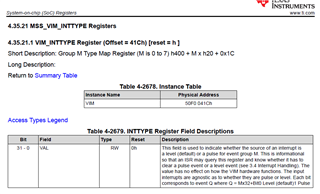

What can be the problem here? Please help.