Hi,

We are currently experiencing a problem with some field units. Our design uses the AM3352BZCZ100 in conjunction with the TPS65217C (PMIC) for power management. The problem we have is that some field units are getting into a non-functional state for which the only way to recover from, is to do a complete power shutdown (i.e. remove the battery, remove the power connected to the AC pin of the PMIC and then reapply power). We use the main power (connected to the AC pin) exclusively for running operation and we use the battery only for time keeping if the system ever goes into a PMIC SLEEP state.

What we could measure/observe on the units that were returned to us is the following:

- External RTC is not running (we measure 1.8V on the XTALIN pin).

- All power rails coming from the PMIC are active and at the default values for the TPS65217C.

- Toggling the state of the WARMRSTn pin (through a push button switch) does not have any effect.

- No activity on the console port (UART0 interface) connected via FTDI.

The above information leads us to believe that we could be stuck in the bootup sequence of the CPU. This hypothesis is based on the following:

- In our application, we use an external 32.768kHz. By default, upon bootup the AM3352 uses the internal 32kHz (derived from internal PLL) for the RTC clock source and the usage of the external source is set during boot.

- Our application uses the AM3352 in Nitro mode (1GHz). This requires that the VDD_MPU be set to 1.325V. This is again set during boot via I2C communication between the AM3352 and the PMIC.

- WARMRSTn is ineffective to reinitialize the unit as it seems that no boot image has been found yet.

We are currently concerned that we could have an issue with the values loaded in the SYSBOOT device lists. We think that improper values might be loaded in the CONTROL_STATUS register for the boot device list which would cause the system to try and find a boot image in a device list that does not contain anything bootable. Unfortunately, since there is no activity on the system at that point, we cannot query the CONTROL_STATUS register to see which values might be loaded.

One question that we have concerns the SYSBOOT latching sequence. In numerous sections of the reference manual, it is stated that the “final” SYSBOOT values are latched at the last rising edge of the PWRONRSTn. However, we can read the following in section 8.1.7.3.2 of the technical reference manual:

“PORz pin at chip boundary gets asserted (goes low). Note: The state of nRESETIN_OUT during PORz assertion should be a don’t care, it should not affect PORz (only implication is if they are both asserted and nRESETIN_OUT is deasserted after PORz you will get re-latching of boot config pins and may see warm nRESETIN_OUT flag set in PRCM versus POR).”

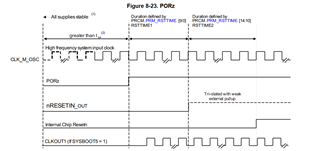

Could you please provide some explanation concerning the highlighted text? From what we can see in the timing diagram of figure 8.23, it seems to be a standard behavior to have the nRESETIN_OUT (WARMRSTn external pin) de-asserted after the PORz (PWRONRSTn external pin):

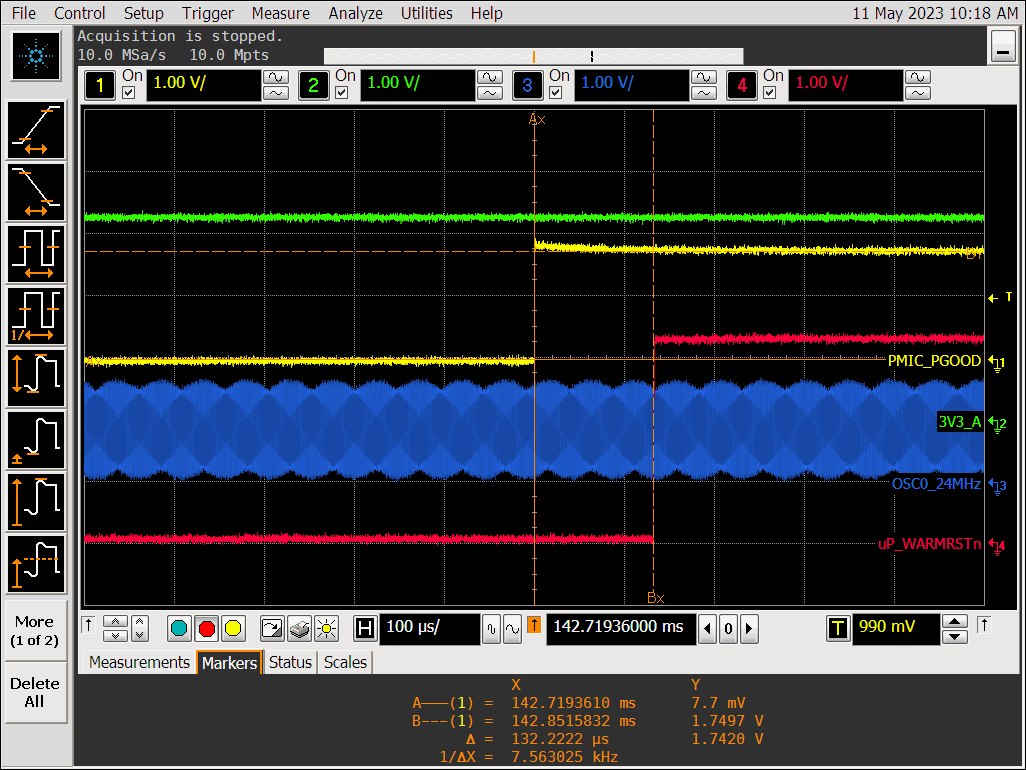

We can also observe this sort of timing on one of our working units:

Could you please help us understand the re-latching condition mentioned in the reference manual (listed above) and provide any other information/questions that could help us investigate this issue further?

Thank you.