Other Parts Discussed in Thread: TDA4VH, TDA4VM

Issue description:

Conducting validation(TDA4VH+LPDDR4 4GB) in Samsung Korea site under mutual customer's request, test case/criteria and test conditions are given from TI(Kevin Scholz) as follows:

|

Test case / pass criteria: Linux memtester [2 instances; 2 loops of 1.2 GB (~ 1 hour)]

o memtester 1200M 2 > /usr/memtester_results/memtester1.txt & o memtester 1200M 2 > /usr/memtester_results/memtester2.txt & o …. <~ 1 hour> o cat /usr/memtester_results/memtester1.txt o cat /usr/memtester_results/memtester2.txt - Pass = no failures reported to the UART terminal

Test conditions:

|

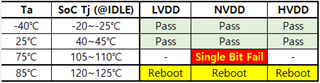

We tested @cold and @room temperature and both passed. But @hot temperature, we set Ta as 75'C and we checked TDA4VH's temp sensor indicating 105~110'C.

And single bit fail happened, and at Ta=85'C, the temp sensor indicated 120~125'C and DRAM rebooted. (We assume this happened because of SOC's throttling)

We have modified some parameters that we could control, but all DOEs failed as follows:

|

Number |

description |

Freq. |

Ta |

SoC Tj (@IDLE) |

LVDD |

NVDD |

HVDD |

|

Pass condition with |

DQ ODT (48ohm), SoC ODT (48ohm), DRAM PDDS (48ohm) |

4266+5%O.C |

75℃ |

105~110℃ |

Single Bit Fail |

- |

- |

|

DOE02 |

DQ ODT (48→80ohm) |

4266+5%O.C |

75℃ |

105~110℃ |

Booting Fail |

- |

- |

|

DOE03 |

DQ ODT (48→120ohm) |

4266+5%O.C |

75℃ |

105~110℃ |

Booting Fail |

- |

- |

|

DOE04 |

SoC ODT (48→80ohm) |

4266+5%O.C |

75℃ |

105~110℃ |

Booting Fail |

- |

- |

|

DOE05 |

SoC ODT (48→120ohm) |

4266+5%O.C |

75℃ |

105~110℃ |

Booting Fail |

- |

- |

|

DOE06 |

DRAM PDDS(48→60ohm) |

4266+5%O.C |

75℃ |

105~110℃ |

Booting Fail |

- |

- |

|

DOE07 |

DRAM PDDS(48→80ohm) |

4266+5%O.C |

75℃ |

105~110℃ |

Single Bit Fail |

- |

- |

Samsung DDR PN: K4FBE3D4HB-KHCL

SW SDK version: 08.06.00.12 (I hope I wrote correctly)

DDR config tool version and the table filled with the paramters of Samesung DDR: Rev. 0.10.0

|

DRAM IO Configuration |

|

||||||||||||||

|

|

|||||||||||||||

|

|

|||||||||||||||

|

|

|

DDRSS0 Values |

DDRSS1 Values |

DDRSS2 Values |

DDRSS3 Values |

|

|

||||||||

|

Parameter Group |

Parameter |

Frequency Set 0 |

Frequency Set 1 |

Frequency Set 2 |

Frequency Set 0 |

Frequency Set 1 |

Frequency Set 2 |

Frequency Set 0 |

Frequency Set 1 |

Frequency Set 2 |

Frequency Set 0 |

Frequency Set 1 |

Frequency Set 2 |

Units |

Notes |

|

VREF Control |

DQ VREF Range |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

- |

2 |

|

DQ VREF |

16 |

16 |

16 |

16 |

16 |

16 |

16 |

16 |

16 |

16 |

16 |

16 |

% of VDDQ |

2 |

|

|

CA VREF Range |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

Range 0 |

- |

2 |

|

|

CA VREF |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

25.6 |

% of VDDQ |

2 |

|

|

Drive Strength |

Pull-Down (PDDS) |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

Ohms |

2, 3 |

|

Pull Up Calibration |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

VDDQ / 3 |

- |

2 |

|

|

Termination |

CA ODT Disable |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

ODT_CA Bond Pad |

- |

2 |

|

CK ODT Override |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

- |

2 |

|

|

CS ODT Override |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

Enable |

- |

2 |

|

|

CA ODT |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

RZQ/4 |

Ohms |

2, 3 |

|

|

DQ ODT |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

Ohms |

2, 3 |

|

|

SOC ODT |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

RZQ/5 |

Ohms |

1, 2, 3 |

|

Other: