Hi,

My customer is asking us about DDR3 design pattern. Could you help to answer to their questions below ?

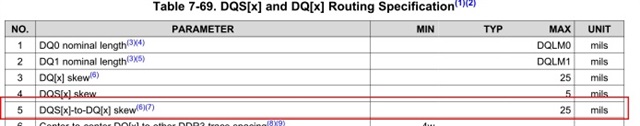

There is the following table in the datasheet.

This table describes that “DQS[x]-to-DQ[x] skew” should be MAX 25 mils”.

Q1) “mils” means “mil” (1mil == 0.0254mm), correct ?

Q2) If so, the difference of thees pattern line length must be less than 25mils (0.635mm), correct ?

If so, the customer thinks that it’s tough requirement. It’s too short.

Q3) Is this stripline ? or micro-stripline ?

Q4) According to the AC timing characteristics, it seems that there is some margin in setup and hold. So, they don't think equal lengths are necessary.

They want to know the formula from which 25mils was derived. Could you tell them ?

Due to board size restrictions, isometric wiring is actually difficult. If this value is applied, even one interlayer via hole will deviate from this value.

Thanks and regards,

Hideaki