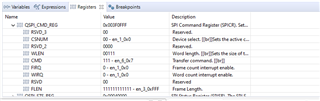

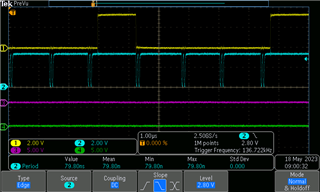

We are using QSPI on the AM4376 to communicated with an FPGA. Although we can communicate to the device, we've found the throughput to be to be unexpectedly low. When looking at signals on a scope, found that QSPI clock was not continuous, but in bursts of two during a single word transfer :

In the above capture, CH1 is CS, CH2 is SCLK, CH3,4 unconnected. We are using 8 bits/word and CLK MODE 3, 10MHz clock.

Are there any settings or combination of settings that can cause SCLK to behave discontinuously, as above?