According to AM64x Sitara Processors datasheer (Rev. E), the AM6442 Pads SERDES0_REFCLK0N & SERDES0_REFCLK0P can be either input or output.

We have a custom design where pcie clock is provided by an external clock generator: one output supplies the SoC, another the bus.

How can we configure the Serdes to utilize this external reference clock?

It appears that the TRM is unclear:

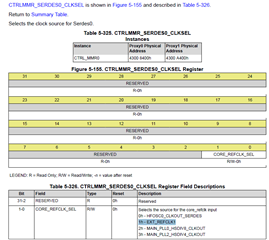

"Section 12.2.3.3 SerDes Integration" offers a choice of 4 options for CTRLMMR_SERDES0_CLKSEL: WKUP_HFOSC0_CLK, HFOSC1_CLK, MAIN_PLL0_HSDIV8_CLKOUT, MAIN_PLL2_HSDIV4_CLKOUT.

Which one of these corresponds to the external inputs?

How do we actually configure this Mux in Linux / U-Boot device-tree?