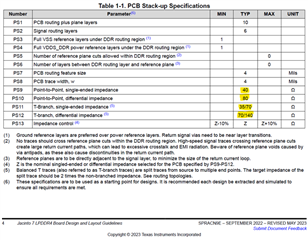

I have some questions regarding your recommendations about the PCB stackup, the LPDDR4 termination, drive strength and PCB trace characteristic impedance in your document “SPRACN9E – SEPTEMBER 2022 – REVISED MAY 2023”. See the following screen shot:

Due to project dependent PCB manufacturing constraints we have used a different stackup (12-layer) with increased impedances (50Ω/100Ω) for our prototype Jacinto LPDDR4 design. The design was successfully simulated and tested. We are now designing the final product and would rather like to transfer our prototype design and not follow the recommendation in your aforementioned document. Therefore my questions:

- Are we allowed to deviate from your recommended trace impedances and use 50Ω/100Ω instead (with appropriate changes to the Jacinto/LPDDR4 drive strength and ODT settings)? We will not reach the doubled impedances after the CA/CLK branches. But we will implement the highest possible impedance and simulate this.

- Are there any hints from you regarding this?

- Any precautions?

- What are the advantages of your low impedance design (besides the possibility to actually reach the doubled impedance after the CA/CLK branches)?

- What are the drawbacks regarding our higher impedance design?

I hope a TI Jacinto/LPDDR4 specialist can help us with this issue.