Other Parts Discussed in Thread: TDA4VH

hello,

I am using TDA4VH EVM board,and i‘m using sdk8.5.

My current task is to shorten the start time of the TDA4VH board Bootloader.

When C71 is not started,the time is

Then I try to analyze the source code,I found that when running tiboot3.bin firmware,there was total of five files will be loaded,They are:

1、bl31.bin //atf

2、bl32.bin //optee

3、ipc_echo_testb_mcu1_0_release_strip.xer5f //in board-support/prebuilt-images/

4、u-boot-spl-nodtb.bin //in board-support/u-boot_build/a72/spl/

5、dt-spl.dtb // in board-support/u-boot_build/a72/dts/

when running tispl.bin firmware,there was total of two files will be loaded,They are:

1、u-boot-nodtb.bin //in board-support/u-boot_build/a72/spl/

2、dt.dtb // in board-support/u-boot_build/a72/dts/

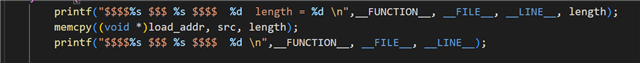

I added their printing before loading their memcpy function before and after,

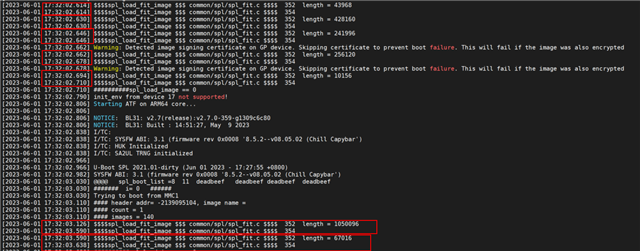

The strange thing is that the 5 files of tiboot3.bin spent a short time, but the two files in memcpy tispl.bin took a long time, you can see from the picture below

I want to know why the memcpy process load u-boot-nodtb.bin will spend 300ms?this time looks too long.

In addition, I also want to ask, what other methods can shorten the operation of Uboot execution time?

thank!