Other Parts Discussed in Thread: TEST2

Dear ti,

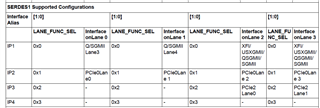

we want to set the serdes1 lane0 SGMII mode, lane1 SGMII mode, lane2 USXGMII mode, lane3 USXGMII mode as the same time

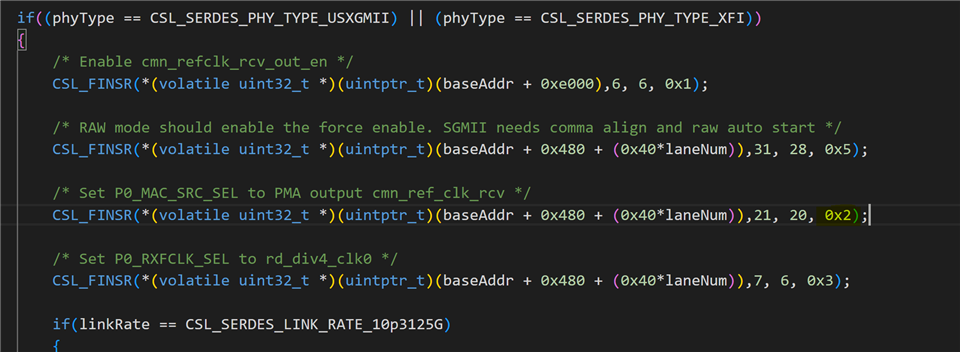

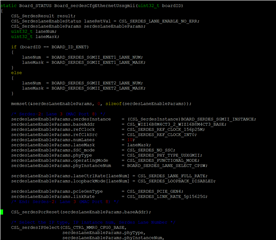

in psdk/pdk_j784s4_08_05_00_37/packages/ti/board/src/j784s4_evm/board_serdes_cfg.c, I can see the USXGMII and SGMII code in separate settings

How to set up serdes1 with USXGMII and SGMII at the same time, thanks