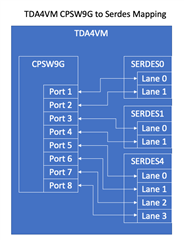

Based on the TRM for the TDA4VM, the CPSW9G (CPSW0) maps each port to a specific serdes and serdes lane.

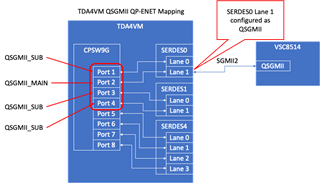

In the QP-ENET expansion, when it is connected to the J7-EVM with TDA4VM, it connects to serdes 0, lane 1. This is called SGMII 2, which makes sense because it is connected to port 2 of CPSW0.

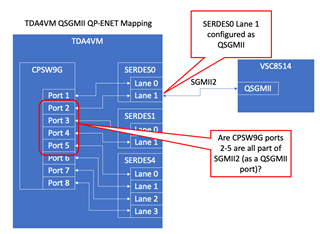

Based on other conversations with TI applications engineering, we understand that when using QSGMII, the specific port used (in this case CPSW0 port 2) and a selection of higher-numbered ports can be part of the QSGMII link. So, in this case ports 2-5. Or ports 2,4,5, and 6 (for example).

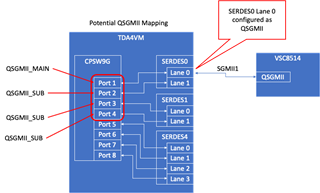

What we understand is the port 1 cannot participate in the QSGMII link. If we wanted to have port 1 in the QSGMII link, then we would have to connect a QSGMII PHY to Serdes0, lane 0. Can you please confirm or clarify this?