Part Number: TDA4VM

Hello TI,

I have a question regarding how the GPIO modules are connected to the internal CBASS bus. From previous discussions I know that CBA is implemented as a crossbar switch. Thereto communication between two bus nodes can take place in parallel without interferences.

For GPIO, the question is which "type of instances" are connected separately to the bus so they can be accessed in parallel?

With "type of instances" I mean the following:

- physical instances for the external pins (WKUP_GPIO0, GPIO0 and GPIO1, in the overview below on the right side)

- virtual instances (WKUP_GPIO0-1, GPIO0-7, below on the left).

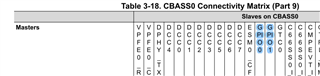

In the connectivity matrix in the TRM it looks like on the bus only the physical instances are connected separately:

But in the same chapter, the virtual modules are listed for the firewall settings:

So if I want to distribute the GPIOs for two different cores in a way that accesses do not cause interferences, what do I have to do?

a) Assign the GPIOs of one core to the physical instance GPIO0, and the other to GPIO1 and/or WKUP_GPIO0

b) Assign the GPIOs to pads regardless of the core that uses it and then map them with the PADCONFIG register to different virtual instances

Best regards

Thomas