Hello,

we have a custom HW design with two ADIN1200 phys connected to ICSSG MDIO pins of the AM6412.

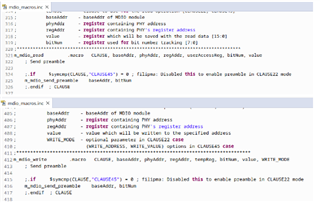

What we observe is that when we use CUST_PHY_read in MANUAL MODE we get just no answer from the phy and therefore no phy is detected by the driver. When we use MDIO_phyRegRead instead (which uses the MDIO module in HW) the phy runs fine.

However we can not use MDIO_phyRegRead for production since it is affected by a known errata (i2329).

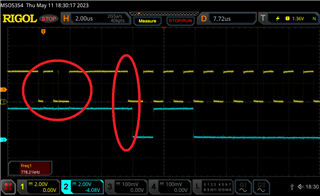

We looked to the MDIO pins and seeing some "strange" behavior:

So my wish would be to either you fix the bitbanging implementation to be compliant to the MDIO Spec or give us the source code that we can fix it ourself.

Kind regards Dennis